一年多来,我们一直惦念着AMD的下一代处理器产品。新的chiplet设计被认为是在驱动性能和可扩展性方面的重大突破,特别是在越来越小的工艺节点上制造高频大芯片变得越来越困难的情况下。AMD预计将通过Ryzen和EPYC在其处理器系列中部署其chiplet范式,这些chiplet每个都有8个下一代Zen 2核心。今天,AMD更详细地介绍了Zen 2核心,为公司上周在Computex上展示的比上一代产品提高15%的时钟性能提供了理由。

AMD的Zen 2产品组合

目前AMD宣布拥有Zen 2核心的产品包括Ryzen第三代消费级CPU,即Ryzen 3000系列,以及AMD下一代企业EPYC处理器,即Rome。到目前为止,AMD已经公布了6款消费级Ryzen 3000处理器的详细信息,包括核心数量、频率、内存支持和电源。关于服务器处理器的细节,除了一些峰值之外,预计将在未来几个月的适当时候公布。

与第一代Zen相比,Zen 2的设计范式已经发生了显著的变化。 新平台和核心实现是围绕台积电7nm工艺的小型8核chiplet设计的,尺寸约74~80平方毫米。在这些chiplet上有两组四核组成的“核心复合体”(CCX),其中包含这4个核心和一组L3缓存——Zen 2的L3缓存是 Zen 1的两倍。

每个完整的CPU,无论它有多少chiplet,都通过Infinity Fabric链路与中央IO芯片配对。IO芯片充当所有片外通信的中心枢纽,因为它包含处理器的所有PCIe通道、内存通道,以及与其他chiplet和其他CPU之间的Infinity Fabric链路。EPYC Rome处理器的IO芯片基于台积电的14nm工艺制造,而消费类处理器IO芯片(体积更小,功能更少)则基于GlobalFoundries的12nm工艺制造。

这款名为“Matisse”(或称Ryzen 3rd Gen、Ryzen 3000系列)的消费级处理器拥有最多两个chiplet,16个内核。AMD将在7月7日推出6个版本的Matisse,从6核到16核不等。6核处理器和8核处理器有一个chiplet,8核以上的处理器有两个chiplet,但在所有情况下IO芯片都是相同的。这意味着每个基于Zen 2的Ryzen 3000处理器都可以访问24个PCIe 4.0通道和双通道内存。根据今天的公告,Ryzen 5 3600的价格将从199美元到16核的700美元以上(我们正在等待这个价格的最终确认)。

基于Zen 2 chiplet构建的EPYC Rome处理器拥有多达8个处理器,使一个平台可以支持多达64个核心。与消费级处理器一样,chiplet不可以直接相互通信——每个chiplet只能直接连接到中央IO芯片。IO芯片包含8个内存通道的链路,以及多达128个PCIe 4.0连接通道。

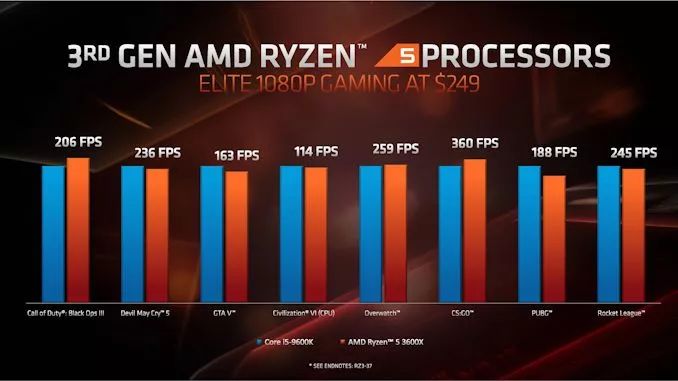

AMD的路线图

在讨论新产品线之前,有必要回顾一下我们目前在AMD的计划路线图中所处的位置。

AMD之前的路线图展示了从Zen到Zen 2、Zen 3的转变,AMD解释说,这个结构已有多年,2017年发布Zen,2019年发布Zen 2,2021年发布Zen 3。节奏并不完全是一年一代,因为这依赖于AMD的设计和制造能力,以及与代工厂合作伙伴的协议和当前的市场力量。

AMD曾表示,Zen 2的计划始终是在7nm工艺上推出,最终使用台积电的7nm制程(Global Foundries未能及时准备好7nm工艺,并最终放弃了这一计划)。下一代Zen 3预计将与更新的7nm工艺保持一致,目前AMD尚未对潜在的“Zen 2+”设计发表任何评论,尽管目前我们并不期望看到它。

除了Zen 3之外,AMD已经声明Zen 4和Zen 5目前正处于各自设计的不同阶段,但是AMD没有承诺特定的时间框架或工艺节点技术。AMD过去曾表示,这些平台和处理器设计的范式都是提前3~5年制定的,公司必须在每一代产品上都下大赌注,以确保自己能够保持竞争力。

为了深入了解Zen 4,在Computex上,AMD嵌入式和半定制组的高级副总裁Forrest Norrod在采访中向AnandTech独家透露了AMD Zen 4 EPYC处理器的代号:Genoa。

Forrest解释说,Zen 5的代号遵循类似的模式,但他不愿对Zen 4产品的时间框架发表评论。鉴于Zen 3的设计预计将在2020年年中推出,如果AMD遵循这一节奏,那么Zen 4将在2021年末/2022年初推出。目前还不清楚它将如何进入AMD的消费级路线图计划,它将取决于AMD如何接近其芯片范式和未来对封装技术的调整,以实现进一步的性能改进。

Zen 2的性能声明

在Computex上,AMD宣布他们已经设计出了Zen 2,当比较相同频率的Zen 2和Zen+时,Zen 2可以提供比Zen+平台高15%的原始性能。与此同时,AMD还声称,在相同的功率下,Zen 2可以提供1.25倍以上的性能增益,或在同样的性能下只有一半的功耗。结合这一点,就特定基准而言,AMD声称其每瓦性能比其上一代产品高75%,比竞争对手高45%。

这些数字我们目前无法核实,因为我们手头没有相关产品,当7月7日禁令解除时,我们会确定基准测试结果。AMD确实花了大量的时间来研究Zen 2微架构的新变化,以及平台级别的变化,以展示该产品与上一代产品相比是如何改进的。

还应该注意的是,在AMD最近的技术日期间,该公司多次表示,他们无意与主要竞争对手在渐进式更新上反复拉锯,试图打败对方,这可能会导致技术停滞不前。AMD的高管们表示,无论竞争对手是谁,AMD都将竭尽所能地挑战每一代产品的性能极限。首席执行官Lisa Su博士和首席技术官Mark Papermaster都表示,他们预计Zen 2产品组合推出的时间表将与竞争激烈的英特尔10nm产品线交叉。尽管情况并非如此,AMD的高管们表示,他们仍在按计划推进他们的路线图。

AMD在展示其即将推出的Matisse处理器的性能时,选择的基准是Cinebench。Cinebench是一种浮点基准测试,该公司在这方面一直做得很好,它倾向于检测CPU FP性能以及缓存性能,尽管它通常不涉及很多内存子系统。

早在今年1月的CES 2019上,AMD就展示了一款未命名的8核Zen 2处理器,与英特尔的高端8核处理器i9-9900K相比,二者在Cinebench R15上的系统得分大致相同,但AMD全系统的耗电量约为英特尔的1/3或更少。在5月份的Computex上,AMD公布了很多8核和12核的细节,以及这些芯片在单线程和多线程Cinebench R20结果中的比较。

AMD表示,在比较不同内核数量时,它的新处理器在CPU基准测试方面提供了更好的单线程性能、更好的多线程性能、更低的功耗和更低的价格。

谈到游戏,AMD在这方面相当乐观。 在1080p时,将Ryzen 7 2700X与Ryzen 7 3800X进行比较,AMD希望帧速率每一代都能有11%~34%的增长。

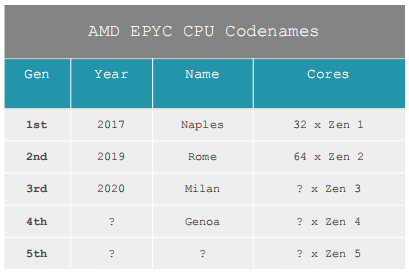

在比较AMD和英特尔处理器时,AMD坚持对热门游戏进行1080p测试,再次比较核心数量和价格类似的处理器。在几乎所有的比较中,AMD的产品和英特尔的产品都不相上下,AMD有的高些,有的低些,或平分秋色。以下以250美元产品为例进行比较:

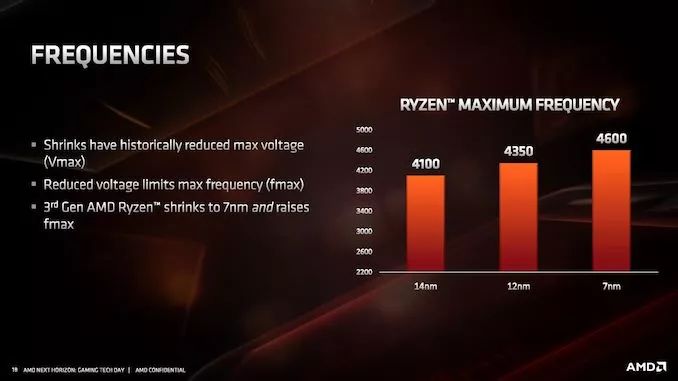

此时,游戏性能旨在展示频率和IPC的改进,而不是展示PCIe 4.0带来的好处。在频率方面,AMD表示,尽管7nm芯片尺寸缩小且通路电阻率较高,但与GlobalFoundries的14nm和12nm相比,它们能够从台积电7nm工艺中获得更高的频率。

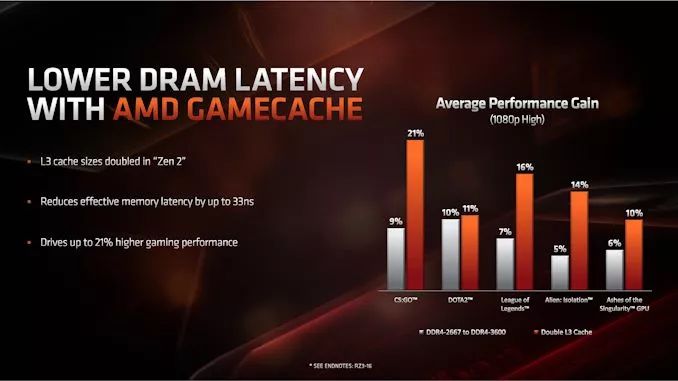

AMD还评论了新的L3缓存设计,因为它从2MB/核心变成了4MB/核心。据AMD称,L3缓存翻了一倍,使用独立GPU进行游戏时,1080p的性能提升了11%~21%。

Zen 2中有一些新指令可以帮助验证这些数字。

Windows优化

对于使用Windows的非英特尔处理器而言,一个令人头疼的关键问题是操作系统中的优化和调度程序安排。我们在过去已经看到Windows对非英特尔微架构布局是多么地不友好,例如AMD以前在Bulldozer中的模块设计、高通在Snapdraon上使用的混合CPU策略,以及最近在Threadripper上进行的多芯片安排,以便将不同的内存延迟域引入消费级计算。

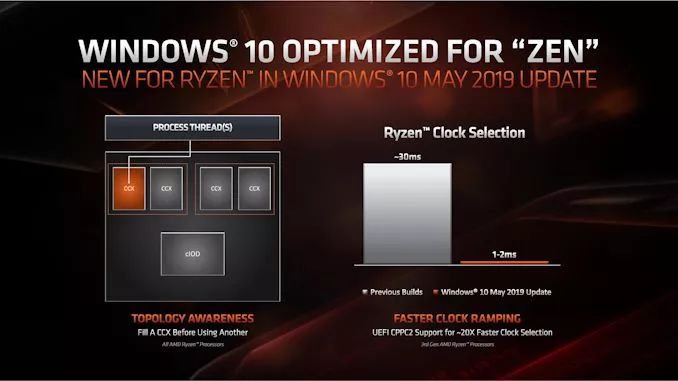

显然,AMD与微软有密切的关系,当涉及到识别处理器的非常规核心拓扑时,这两家公司致力于确保线程和内存分配,没有程序驱动的方向,试图最大限度地利用系统。随着5月10日Windows的更新,一些额外的功能已经到位,以充分利用即将到来的Zen 2微架构和Ryzen 3000芯片布局。

优化有两方面,这两方面都很容易解释。

线程分组

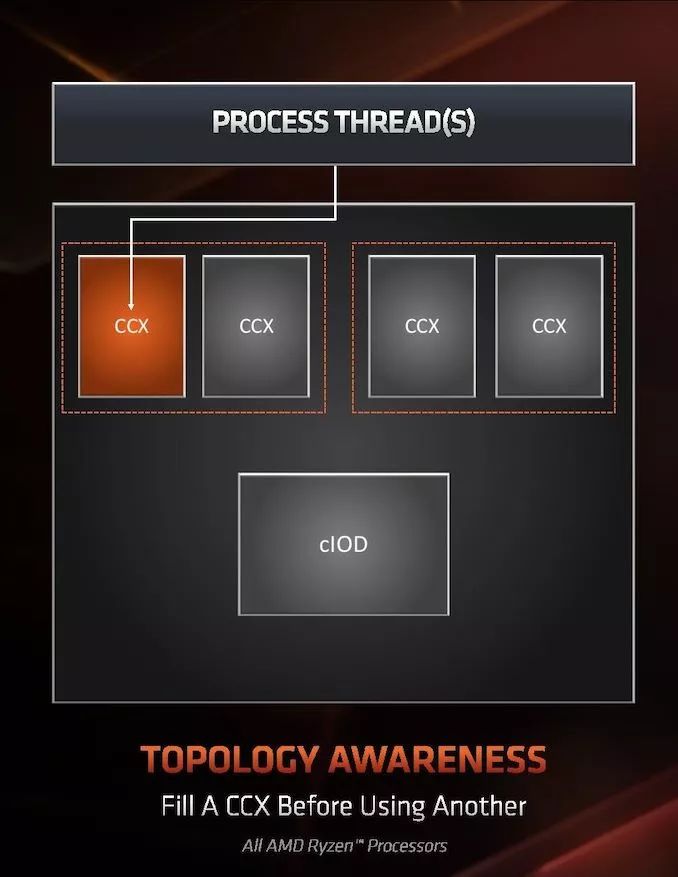

第一个是线程分配。当处理器具有不同的CPU核心“组”时,分配线程的方式也就不同,所有这些方法都有各自的优缺点。线程分配的两个极端归结为线程分组和线程扩展。

线程分组是当新线程生成时,它们将被直接分配到已经拥有线程的内核旁边的内核上。这使线程紧密结合在一起,用于线程到线程的通信,但是它可以创建高功率密度的区域,特别是当处理器上有多个内核但只有几个处于活动状态的时候。

线程扩展是指内核彼此放置得尽可能远。这意味着第二个线程尽可能远地在不同的chiplet或不同的核心复合体(CCX)上产生。这允许CPU通过没有高功率密度的区域来保持高性能,通常在多个线程上提供最佳的turbo性能。

线程扩展的危险在于,当一个程序生成两个线程,而这两个线程最终位于CPU的不同位置的时候。在Threadrapper中,这甚至可能意味着第二个线程位于CPU的一个具有较长内存延迟的部分,从而导致两个线程之间的潜在性能不平衡,即便这些线程所在的内核处于较高的turbo频率。

由于现代软件(特别是视频游戏)正在产生多线程而不是依赖单个线程,并且这些线程需要相互通信,AMD正在从混合线程扩展技术转向线程分组技术。这意味着在访问另一个CCX之前,一个CCX将被线程填满。AMD认为,尽管一个chiplet中具有高功率密度的潜力,而另一个可能处于非活动状态,但对于整体性能而言,这仍然是值得的。

对于Matisse而言,这应该可以为有限的线程场景提供一个很好的改进。看看这对即将到来的EPYC Rome CPU或未来的Threadripper设计有多大影响将会很有趣。AMD在其解释中提供的单一基准是1080p Low的《火箭联盟》,报告称帧速率增加了15%。

时钟提升

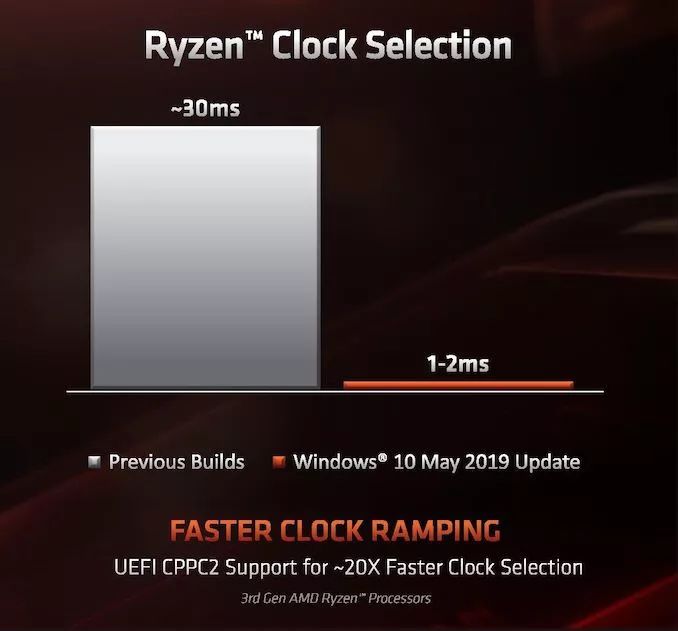

对于熟悉Skylake微架构的用户来说,你可能还记得英特尔推出了一项名为Speed Shift的新功能,使处理器能够更自由地在不同P状态之间进行调整,以及非常快速地从空闲调整到负载——Skylake的第一个版本从100毫秒到40毫秒,然后Kaby Lake下降到15毫秒。它通过将P状态控制从操作系统返回给处理器来实现这一点,处理器根据指令吞吐量和请求做出反应。在Zen 2中,AMD现在实现了相同的功能。

相比于英特尔,AMD在频率调整方面已经具有足够的粒度,允许25MHz而不是100MHz的差异,但是,当涉及非常突发驱动的工作负载(burst-driven workload)时,能够实现更快的ramp-to-load频率跳变将给AMD带来帮助,例如WebXPRT(英特尔最喜欢这种演示)。根据AMD的说法,使用Zen 2实现这一功能的方式将需要BIOS更新以及Windows 5月10日的更新,但是它将把Zen的频率提升时间从30毫秒降低到Zen 2的1~2毫秒。值得注意的是,这比英特尔给出的数字要快得多。

AMD实现的技术名称涉及CPPC2,即Collaborative Power Performance Control 2,AMD的指标表明这会增加突发工作负载和应用程序负载。AMD表示,使用PCMark10的应用程序启动子测试,应用程序的启动时间性能提升了6%。

增强了Zen 2的安全性

Zen 2的另一个方面是AMD用来提高现代处理器安全性要求的方法。正如已经报道过的,最近一系列的侧通道攻击并没有影响AMD处理器,这主要是因为AMD管理其TLB缓冲区的方式,这些缓冲区在大部分成为问题之前总是需要额外的安全检查。尽管如此,对于AMD易受攻击的问题,它已经为这些问题实现了一个完全基于硬件的安全平台。

这里的变化来自Speculative Store Bypass,称为Spectre v4,AMD现在有额外的硬件与操作系统或虚拟内存管理器(如hypervisor)协同工作,以便进行控制。AMD预计这些更新不会带来任何性能变化。诸如Foreshadow和Zombieload等新问题不会影响AMD处理器。

新指令

缓存和内存带宽QoS控制

与大多数新的x86微架构一样,存在通过新指令提高性能的动力,但也会尝试在支持哪些指令方面实现不同供应商之间的对等。对于Zen 2,虽然AMD没有像英特尔那样迎合一些更古怪的指令集,但它在三个不同的领域增加了新的指令。

第一个是CLWB,以前已经在英特尔处理器上看到过它与非易失性内存有关。 此指令允许程序将数据推回到非易失性内存中,以防系统收到停机命令造成数据丢失。尽管AMD没有明确说明,但还有其他与保护数据到非易失性内存系统相关的指令。这可能表明AMD正在寻求在未来的设计中更好地支持非易失性内存的硬件和结构,特别是在EPYC处理器中。

第二个缓存指令WBNOINVD是一个仅限AMD的命令,但它基于其他类似的命令,如WBINVD。 此命令用于预测将来可能需要缓存的特定部分,并清除它们,以便加速将来的计算。如果所需的缓存行未准备就绪,则会在所需操作之前处理刷新命令,从而增加延迟——当延迟关键型指令仍沿流水线中传递时提前运行缓存行刷新,有助于加速其最终执行。

在QoS下归档的最后一组指令实际上与如何分配缓存和内存优先级有关。

当针对不同客户将云CPU拆分为不同的容器(container)或虚拟机(VM)时,性能级别并不总是一致的,因为性能可能会根据另一个虚拟机在系统上执行的操作而受到限制。这就是所谓的“嘈杂邻居”问题:如果其他人正在占用所有核心到内存的带宽(即L3缓存),那么系统上的另一个VM就很难访问它所需的内容。由于这个嘈杂的邻居,其他VM在处理其工作负载时的延迟将是高度可变的。或者,如果一个任务关键型VM在系统上,而另一个VM一直在请求资源,那么任务关键型VM可能会错过它的目标,因为它没有访问所需的所有资源。

除了确保单个用户可以完全访问硬件之外,处理嘈杂的邻居很困难。大多数云提供商和操作甚至不会告诉你是否有邻居,在实时VM迁移的情况下,这些邻居可能会非常频繁地更改,因此不能保证在任何时候都有持续的性能。这就需要一组专用的QoS(服务质量)指令。

与英特尔的实现一样,当一系列虚拟机分配到虚拟机管理程序之上的系统上时,虚拟机管理程序可以控制每个虚拟机有多少内存带宽和缓存。如果任务关键型8核虚拟机需要访问64MB的L3和至少30GB/s的内存带宽,则虚拟机监控程序可以控制优先级虚拟机始终有权访问该数量,并将其从其他虚拟机的池中完全删除,或者在任务关键型虚拟机突然进入完全访问时智能地限制其要求。

英特尔只在其Xeon可扩展处理器上实现了这一功能,但AMD将为消费级和企业用户在Zen 2处理器系列中实现这一功能。

我在这个功能上遇到的最直接的问题是在消费级方面。想象一下,如果一个视频游戏需要访问所有的缓存和所有的内存带宽,而一些流媒体软件却不能访问——这可能会对系统造成严重的破坏。AMD解释说,虽然从技术上讲,单个程序可以请求一定级别的QoS,但是,这些请求是否有效和合适将取决于操作系统或虚拟机监控程序。他们将此功能更多地视为发挥虚拟机监控程序作用时使用的一种企业功能,而不是消费级系统上的裸机安装。

CCX尺寸

向下移动节点大小会在核心内外带来许多挑战。即使不考虑功率和频率,将结构放入芯片,然后将芯片集成到封装中,以及通过正确的连接为芯片的正确部分提供电力本身也成为一种练习。AMD让我们深入了解7nm如何改变其部分设计,以及其中的封装挑战。

AMD放弃的一个关键指标与核心复合体(CCX)有关:4个核心,相关的核心结构,然后是L2和L3缓存。AMD称,在12 nm和ZEN+核心的情况下,单个核心复合体为60平方毫米,其中核心占44平方毫米,8MB的L3占16平方毫米。把其中两个60平方毫米的复合体加上两个带内存控制器、PCIe通道、4个IF链路和其他IO,Zen+ Zeppelin裸片总共是213平方毫米。

对于Zen 2,单个chiplet是74平方毫米,其中31.3平方毫米是核心复合体,有16 MB的L3。AMD没有将这31.3个数字拆分为核心和L3,但是人们可以想象L3可能接近这个数字的50%。chiplet如此小的原因是它不需要内存控制器,它只有一个IF链路,没有IO,因为所有的平台要求都在IO芯片上。这使得AMD可以使chiplet非常紧凑。然而,如果AMD打算继续增加L3缓存,那么L3缓存可能会占据芯片的大部分。

但总体而言,AMD已经表示CCX(核心加L3)的尺寸减少了47%。这显示了巨大的可扩展性,特别是当+15%的原始指令吞吐量和增加的频率开始发挥作用时。每平方毫米的性能将是一个非常令人兴奋的指标。

封装

由于Matisse使用AM4插槽,Rome使用EPYC插槽,AMD表示他们必须押宝封装技术,以保持兼容性。这些赌注中的一些最终总是为了持续的支持而进行权衡,但AMD相信,为了兼容性值得付出额外的努力。

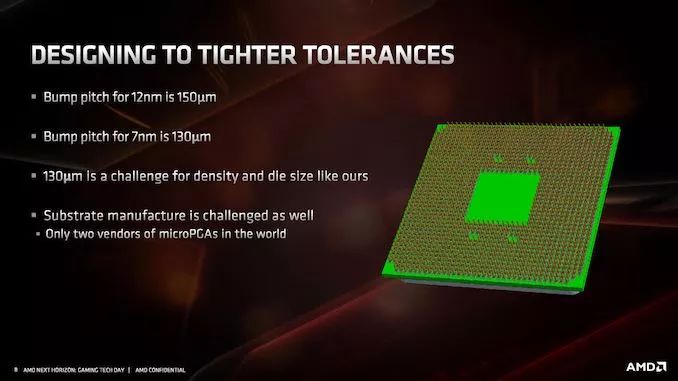

AMD谈到的与封装有关的关键问题之一是,每个裸片如何连接到封装上。为了实现pin-grid阵列台式机处理器,必须以BGA方式将芯片固定到处理器上。AMD表示,由于采用了7nm工艺,凸点间距(裸片和封装上的焊球之间的距离)从12nm的150微米减少到7nm的130微米。这听起来并不多,但AMD表示,世界上只有两家厂商拥有足够的技术来做到这一点。唯一的替代方案是使用更大的芯片来支持更大的凸点间距,最终导致芯片中出现大量空闲(或不同的设计范式)。

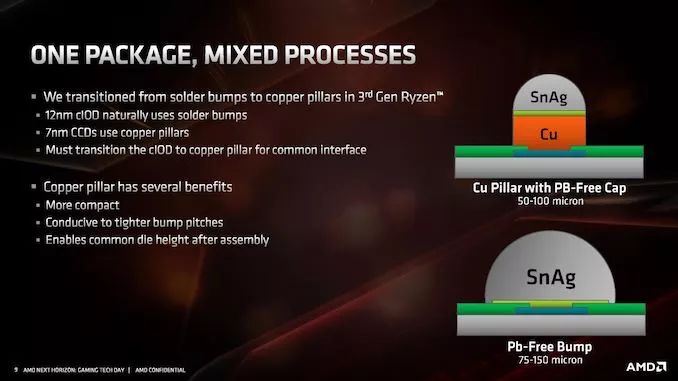

为了实现更紧密的凸点间距,其中一种方法是调整在芯片下侧处理凸点的方式。通常情况下,封装上的焊料凸点是一个无铅焊料的团或球,依靠表面张力和回流的物理特性来确保其一致且规则。然而,为了实现更紧密的凸点间距,AMD必须转向铜柱焊料凸点拓扑。

为了实现这一特性,铜被外延沉积在掩模内,以便形成回流焊料所使用的“支架”。由于焊柱的直径,所需的掩模较少,从而产生较小的焊料半径。由于其在Matisse内部的双芯片设计,AMD还遇到了另一个问题:如果IO芯片使用标准焊料凸点掩模,并且chiplet使用铜柱,则集成散热器需要有一定的高度一致性。对于较小的铜柱,这意味着管理铜柱的增长水平。

AMD解释说,与建造不同高度的散热器相比,实际上管理这种连接实现更容易,因为散热器的冲压工艺不会产生如此小的公差。AMD预计,未来所有7nm设计都将采用铜柱实现。

布线

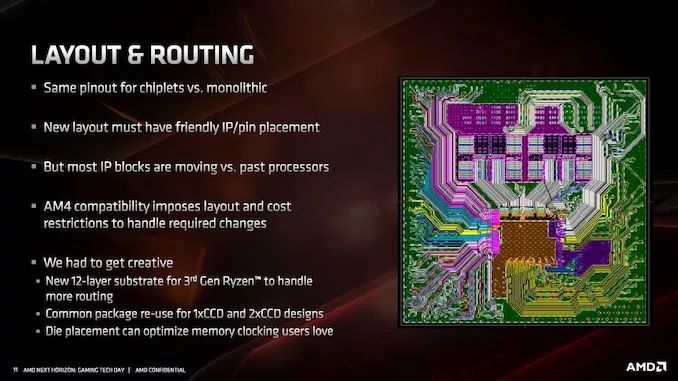

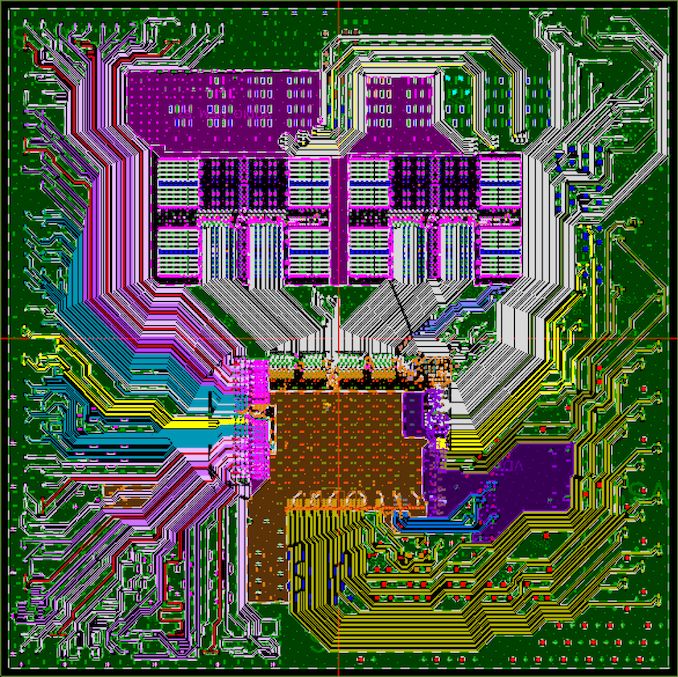

除了将裸片放在有机衬底上之外,该衬底还必须管理裸片与裸片外部之间的连接。为了处理额外的布线,AMD必须将封装中的衬底层增加到12层(没有透露在Rome需要多少层,也许14层)。对于单核chiplet和双核chiplet处理器而言,这也变得有些复杂,特别是在将裸片放进封装之前对其进行测试时。

从图中我们可以清楚地看到从两个chiplet到IO芯片的IF链路,IO芯片也处理内存控制器以及貌似电源平面的任务。chiplet之间没有封装内链接:chiplet无法直接通信,chiplet之间的所有通信都是通过IO芯片处理的。

AMD表示,采用这种布局,他们还必须注意处理器如何放置在系统中,以及冷却和内存布局。此外,当涉及到更快的内存支持或PCIe 4.0更严格的容差时,所有这些也需要被考虑,以便在不受其他布线干扰的情况下为信号传导提供最佳路径。

AMD Zen 2微架构概述

快速分析

在AMD的技术日,在场的是同事兼首席架构师Mike Clark,他经历了这些变化。Mike是一个很好的工程师,尽管总是让我感到有趣的是,谈论最新产品上市的工程师们已经在公司工作了一代、两代或三代(对于任何公司都是这样,不仅仅是AMD)。Mike说,他花了一段时间来回想Zen+到Zen 2的具体变化,而他的脑海中已经经历了几代产品的变化。

Zen 2的一个有趣元素是围绕其意图。最初Zen 2仅仅是Zen+的缩小版,从12nm缩小到7nm,类似于我们在本世纪初看到的英特尔的tick-tock模型。然而,AMD根据内部分析和7nm的时间框架,决定使用ZEN 2作为性能更好的平台,以多种方式利用7nm,而不是仅仅在一个新的工艺节点上重新设计相同的布局。作为调整的结果,AMD正在推动Zen 2的IPC比Zen+提升15%。

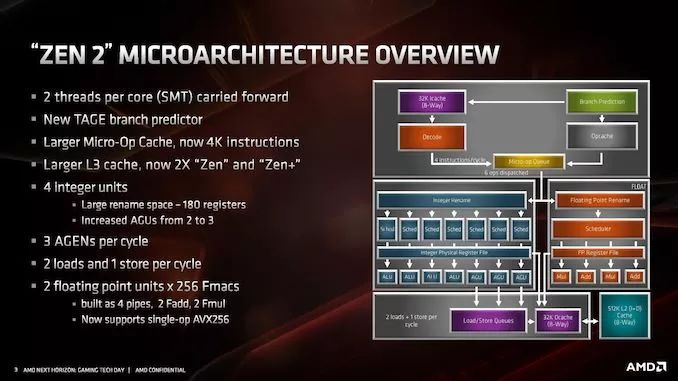

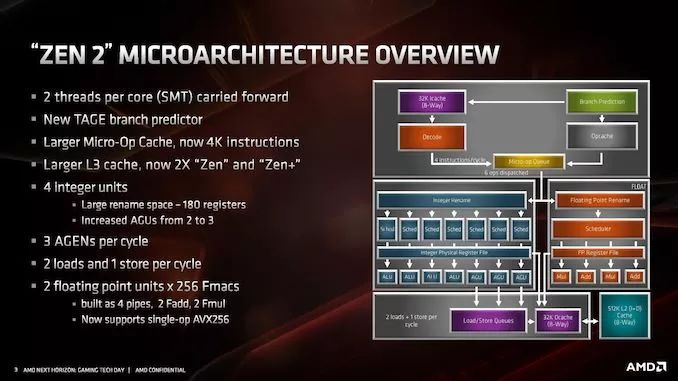

当谈到微架构的确切变化时,我们基本上看到的仍然是类似于Zen外观的布局规划。Zen 2是Zen系列的一员,在处理x86方面并不是完全的重新设计或不同的范例——与其他具有家族更新的架构一样,Zen 2提供了更有效的核心和更广泛的核心,允许更好的指令吞吐量。

从较高的层面来看,核心看起来非常相似。Zen 2设计的亮点包括不同的L2分支预测器,称为TAGE预测器,micro-op缓存加倍,L3缓存加倍,整数资源增加,加载/存储资源增加,以及对单操作AVX-256(或AVX2)的支持。AMD表示,基于其能量感知频率平台,AVX2没有频率损失。

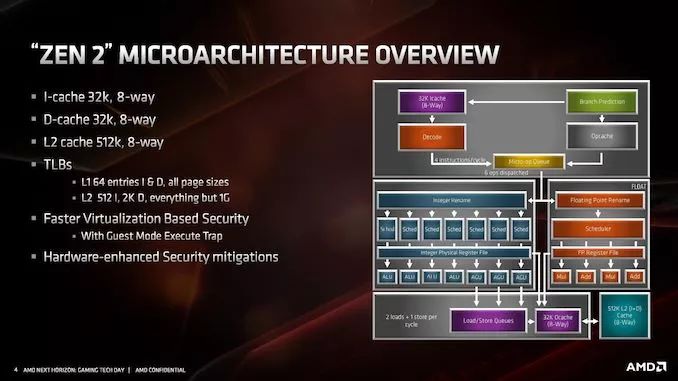

AMD还对缓存系统进行了调整,其中最引人注目的是L1指令缓存,它被减半到32kb,但关联性增加了一倍。进行这种更改是出于重要的原因,我们将在下一页中对此进行讨论。L1数据缓存和L2缓存保持不变,但是事务后备缓冲区(TLB)增加了支持。AMD还表示,它已经在安全方面增加了更深层次的虚拟化支持,有助于实现流水线后续的功能。正如本文前面提到的,还有安全性强化更新。

对于快速分析,可以很容易地看出,在许多情况下,加倍micro-op缓存将为IPC带来显著的改进,而把它与负载/存储资源的增加相结合,会有助于通过更多的指令。加倍L3缓存有助于特定工作负载,支持AVX2单操作也是如此,但改进的分支预测程序也将展示原始性能提升。总而言之,从纸面分析来看,AMD 15%的IPC改进似乎是一个非常合理的数字。

在接下来的几页中,我们将深入探讨微架构的变化。

提取/预提取

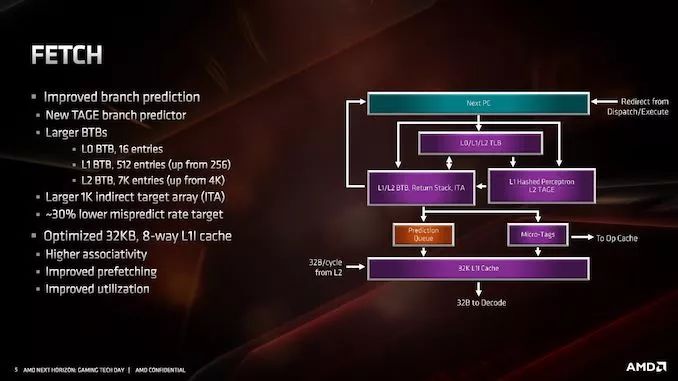

我们从处理器的前端开始,预取器。

AMD在这里宣传的主要改进是使用TAGE预测器,尽管它只用于非l1提取。这听起来可能并不足道:AMD仍然使用哈希感知器预取引擎为L1提取,这将会尽可能多的提取,但TAGE L2分支预测器使用额外的标记来实现更长的分支历史,以获得更好的预测路径。这对于L2预取及以后的预取变得更加重要,哈希感知器优先用于基于功率的L1中的短预取。

在前端,我们还有更大的BTB,以帮助跟踪指令分支和缓存请求。L1 BTB的大小增加了一倍,从256个条目增加到512个条目,L2几乎增加了一倍,从4K增加到7K。L0 BTB保持在16个条目,但间接目标阵列最多可达1K个条目。总体而言,AMD的这些变化让误预测率降低了30%,从而节省了电力。

另一个主要变化是L1指令缓存。我们注意到它对于Zen 2来说更小:只有32KB而非64KB,但是关联性增加了一倍,从4路增加到8路。考虑到高速缓存的工作方式,这两种影响最终不会互相抵消,但是32KB L1-I缓存应该更节能,并且有更高的利用率。L1-I缓存并不是孤立地减少的——减少I缓存大小的好处之一是允许AMD将micro-op缓存的大小增加一倍。这两个结构在核心内部彼此相邻,因此即使在7nm,我们也有空间限制的实例,导致核心内部结构之间的权衡。AMD表示,这种较小的L1与较大的micro-op缓存的配置,在更多的测试场景中表现更好。

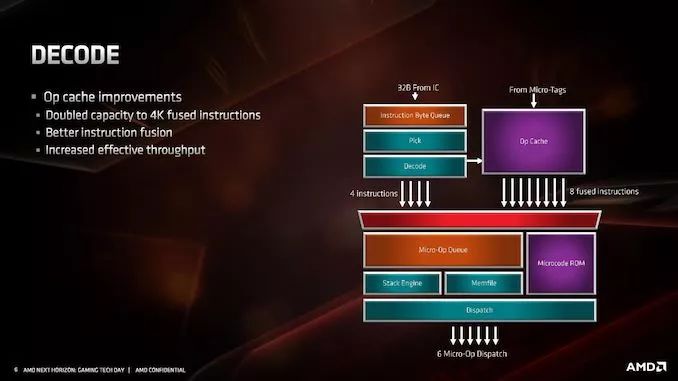

解码

对于解码阶段,这里的主要提升是micro-op缓存。通过把2K条目加倍到4K条目,它将比以前包含更多的解码操作,这意味着它将经历大量的重用。为了便于使用,AMD提高了从micro-op缓存到缓冲区的调度速度,最多8条融合指令。假设AMD可以经常绕过它的解码器,这应该是一个非常有效的区块。

4K条目更令人印象深刻的是当我们将它与竞争对手进行比较的时候。在英特尔的Skylake系列中,这些内核中的micro-op缓存只有1.5K条目。英特尔将Ice Lake的规模增加了50%,达到了2.25K,这个核心将在今年晚些时候进入移动平台,明年可能进入服务器。相比之下,AMD的Zen 2核心将涵盖从消费级到企业的所有领域。同时,我们也可以将其与Arm A77 CPU的micro-op缓存进行比较,该缓存为1.5K条目,然而,它是Arm为核心设计的第一个micro-op缓存。

Zen 2中的解码器保持不变,我们仍然可以访问4个复杂解码器(Intel是1个复杂解码器+4个简单解码器),解码指令被缓存到micro-op缓存中,并被分派到micro-op队列中。

AMD还表示,它已经改进了其micro-op融合算法,但没有详细说明这将如何影响性能。目前的micro-op融合转换已经相当好,所以看看AMD在这里做了什么将会很有趣。与ZEN和ZEN+相比,基于对AVX2的支持,这意味着解码器不需要将AVX2指令分解为两个micro-op:AVX2现在是通过流水线的单个micro-op。

除了解码器之外,micro-op队列和调度可以在每个周期向调度器馈送6个micro-op。但是,这有点不平衡,因为AMD有独立的整数和浮点调度器:整数调度器每周期可以接受6个micro-op,而浮点调度器只能接受4个micro-op。然而,调度可以同时向两者发送micro-op。

浮点

浮点性能的关键亮点是完全支持AVX2。AMD已经将执行单元的宽度从128位增加到256位,允许单周期AVX2计算,而不是将计算分成两个指令和两个周期。这是通过提供256位负载和存储来增强的,因此FMA单元可以连续馈送。AMD指出,由于其能量感知调度,在使用AVX2指令时没有预定义的频率下降(但是频率可能会根据温度和电压要求而降低,但无论使用何种指令,这都是自动的)。

在浮点单元中,队列每个周期最多接受来自调度单元的4个micro-op,这些micro-op馈入一个包含160个条目的物理寄存器文件。这将移动到4个执行单元,可以在加载和存储机制中向这些单元提供256b的数据。

除了尺寸加倍之外,FMA还进行了其他调整。AMD表示,他们提高了内存分配、重复物理计算,以及某些音频处理技术的原始性能。

另一个关键更新是将FP乘法延迟从4个周期减少到3个周期。这是相当显著的进步。AMD表示,公司对很多细节保密,因为公司想在8月的Hot Chips上展示。我们将在7月7日进行全面的指令分析。

整数单元、加载和存储

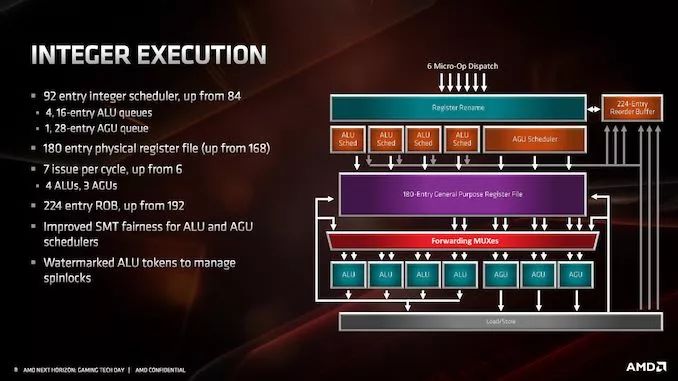

整数单元调度器每个周期最多可以接受6个micro-op,这些micro-op将馈送到224个条目的重新排序缓冲区(以前是192个)。整数单元在技术上有7个执行端口,由4个ALU(算术逻辑单元)和3个AGU(地址生成单元)组成。

调度程序由4个16条目的ALU队列和1个28条目的AGU队列组成,尽管AGU单元每个周期可以向寄存器文件馈送3个micro-op。基于AMD对通用软件中指令分布的模拟,AGU队列的大小有所增加。这些队列馈送180个条目的通用寄存器文件(原先是168个),但也跟踪特定的ALU操作,以防止潜在的停机操作。

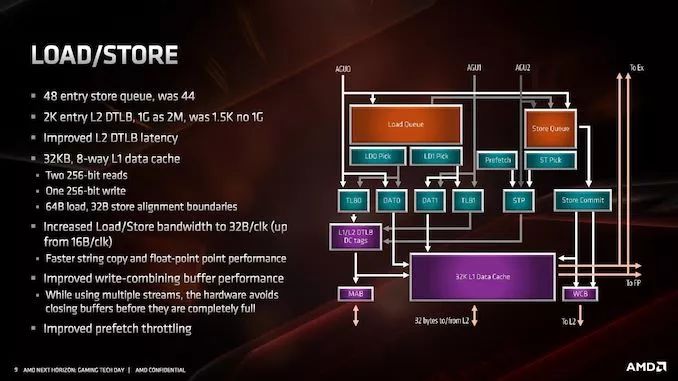

三个AGU馈送到加载/存储单元,加载/存储单元每个周期可以支持两个256位的读取和一个256位的写入。从上图可以看出,并非所有三个AGU都相同:AGU2只能管理存储,而AGU0和AGU1可以同时进行加载和存储。

存储队列从44个条目增加到48个条目,数据缓存的TLB也增加了。不过,这里的关键指标是加载/存储带宽,因为核心现在每个时钟可以支持32个字节,而非原来的16个字节。

缓存和Infinity Fabric

缓存中最大的变化就是L1指令缓存,它从64KB减少到了32KB,但是结合度从4路增加到了8路。这一变化使AMD能够将micro-op缓存的大小从2K条目增加到4K条目,AMD认为这可以更好地平衡现代工作负载的发展。

L1-D缓存仍然是8路32KB ,而L2缓存仍为8路512KB。L3缓存是非包容性缓存(L2是包容性缓存),现在它的大小已经增加了一倍,达到16MB/核心复合体(原先是8MB)。AMD管理L3的方式是每个CCX共享一个16MB的区块,而不是允许从任何核心访问L3。

由于L3的大小增加,延迟略有增加。L1仍然是4周期,L2仍然是12周期,但是L3已经从35周期增加到了40周期(这是大缓存的一个特性,它们的延迟会稍微长一些;这是一个有趣的权衡)。AMD已经声明它已经增加了处理L1和L2丢失的队列的大小,尽管尚未详细说明它们现在有多大。

Infinity Fabric

随着Zen 2的推出,我们也转向了第二代Infinity Fabric。IF2的主要更新之一是支持PCIe 4.0,因此总线宽度从256位增加到512位。

据AMD称,IF2的整体效率提高了27%,导致每比特的功耗更低。随着EPYC中的IF链路越来越多,这将变得非常重要,因为数据从chiplet传输到IO芯片。

IF2的一个特点是时钟已经从DRAM主时钟中分离出来。在Zen和Zen+中,IF频率与DRAM频率耦合,这导致了一些有趣的场景,在这些场景中,内存可以运行得更快,但IF中的限制意味着它们都受到时钟锁步特性的限制。对于Zen 2,AMD已经为IF2引入了比率,支持1:1的正常比率或2:1的比率,可以将IF2时钟减半。

这个比率应该在DDR4-3600或DDR4-3800附近自动发挥作用,但这确实意味着IF2时钟减少了一半,这对带宽有冲击效应。应该注意的是,即使DRAM频率很高,如果IF频率较慢,则可能会限制从该较快内存获得的原始性能增益。AMD建议在DDR4-3600附近保持1:1的比例,而是在该速度优化sub-timing。

构建像Zen 2这样的核心需要的不仅仅是构建核心。核心、SoC设计和平台之间的相互作用要求不同的内部团队联合起来,创造出单独工作所缺乏的协同水平。AMD在chiplet设计和Zen 2方面所做的工作表现出了巨大的希望,不仅可以利用更小的工艺节点,还可以为计算的未来开辟一条道路。

当进入更先进的工艺节点时,主要优点是功耗更低。这可以通过以下几种方式来实现: 在相同的性能下降低运行的功率,或者使用更多的功率预算来做更多的事情。随着时间的推移,我们在核心设计中看到了这一点:随着更多的功率预算被开启,以及内核中的不同单元变得更高效,额外的功率被更广泛地用来驱动内核,希望能提高原始指令速率。这不是一个容易解决的问题,因为存在许多权衡因素:Zen 2核心中的一个例子就是L1 I缓存的减少使得AMD的micro-op缓存增加了一倍,AMD希望这样能提高性能和功耗。对这些工程师来说,实施至少在高层次上可行的方案就像玩乐高一样。

尽管如此,Zen 2看起来很像Zen。它属于同一个系列,这意味着它看起来非常相似。AMD在这个平台上所做的一切,启用PCIe 4.0,并使服务器处理器摆脱类似NUMA的环境,都将有助于AMD的长远发展。AMD良好的前景取决于它可以驱动的服务器部件的频率有多高,但Zen 2+ Rome将会着力解决Zen的客户提出的大量问题。

总之,AMD已经在Zen 2和Zen+的基础上提高了15%的核心性能。随着核心的变化,在高层次上看肯定是可行的。 专注于性能的用户会喜欢新的16核Ryzen 9 3950X,而处理器在105W时看起来效率很高,因此看看它在低功耗下会发生什么会很有趣。我们也期待在接下来的几个月内Rome推出非常强大的产品,特别是像双倍FP性能和QoS这样的特性,64核的原始多线程性能将成为市场的一个有趣的破坏者,特别是价格有效的话。

程序员和搬砖者,开发研制FPGA开发板和芯片CPU, 奇门遁甲,阴阳五行,周易八卦的学习者