RISC-V产业生态已经进入快速发展期,随着大量的公司进入到RISC-V技术领域,基于RISC-V架构的芯片也如雨后春笋般涌入市场。可以预见的是,RISC-V的时代正在到来。

当下的芯片市场,以x86、MIPS、ARM、RISC-V四种主流指令集/芯片架构为主,其中最为常见还是x86以及ARM。在AI热潮的推动下,RISC-V近年来正在飞速发展,其作为一种全新的、简单且开源免费的指令集架构则是实现突破限制的最佳选择。

RISC-V+FPGA——全新发展方向

RISC-V处理器和FPGA的生态环境非常匹配,RISC-V的出现恰好给FPGA新的选择和发展方向,包括SoC FPGA发展、实现软硬件都可编程以及拓宽FPGA应用领域,其必将会在SoC FPGA生态里面发挥重要作用。

在此背景下,以及在中国科学院计算技术研究所的大力支持下,英特尔FPGA中国创新中心运营方重庆海云捷迅科技有限公司不懈攻关,于2021年9月实现了RISC-V处理器在FPGA上的成功部署,并正确控制其外设功能,踏出了在“RISC-V+FPGA”发展道路上的第一步。

技术背景——NutShell处理器

选用的RISC-V处理器是由中国科学院大学与中国科学院计算技术研究所发布的首期“一生一芯”计划成果-果壳NutShell处理器。果壳处理器是使用Chisel语言模拟化设计的,基于RISC-V RV64开放指令集的顺序单发射处理器实现。

果壳NutShell处理器基于9级流水线顺序设计。存储系统方面,果壳NutShell处理器包含一级指令缓存和数据缓存及可选的二级缓存。处理器通过AXI4总线与外界相连。果壳NutShell处理器支持M、S、U三个特权级,支持I、M、A、C、Zicsr与Zifencei指令扩展,支持虚实地址转换,包含页表缓冲(TLB)以加速地址转换过程,支持Sv39分页方案。

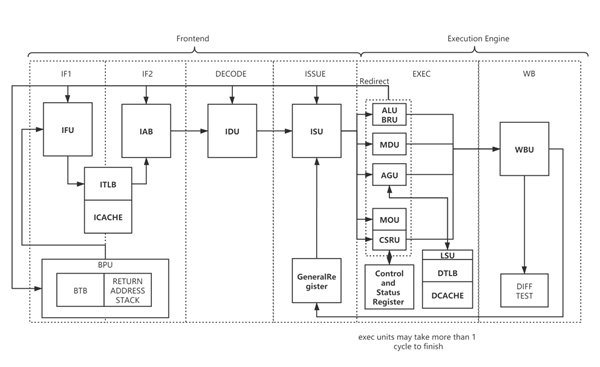

图一果壳NutShell处理器整体微结构设计图

果壳NutShell处理器的设计由三部分组成:负责分支预测和取指的前端(Front-end),负责执行指令的执行引擎(Execution Engine,也称后端Back-end),以及用于访存操作的访存单元(LSU)。前端完成取指与译码操作后会将指令放置在译码缓冲区中。后端从译码缓冲区中读出指令并顺序执行。访存单元作为一个功能单元(FU)包含在后端流水线中。控制逻辑分布在流水线的各个部分。

技术背景——Cyclone®V SoC FPGA

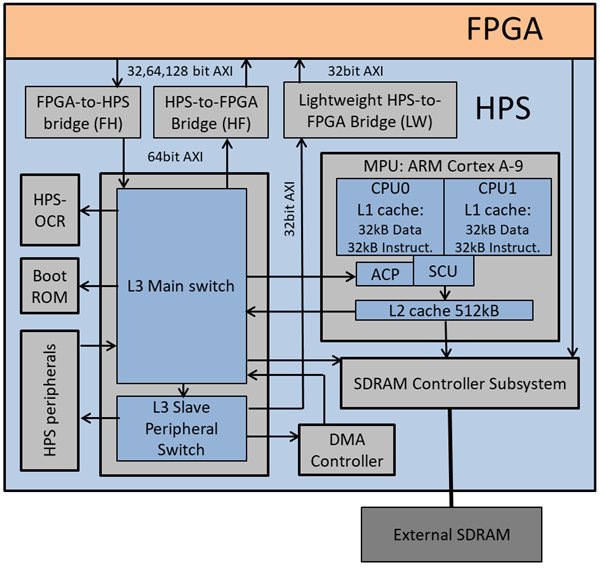

选用的FPGA芯片是由Intel发布的一款在单一芯片上集成了双核的ARM Cortex-A9处理器和FPGA逻辑资源的SoC芯片-Cyclone®V SoC FPGA芯片。该芯片相较于传统的单一ARM处理器或FPGA芯片,既拥有了ARM处理器灵活高效的数据运算和事务处理能力,同时又集成了FPGA的高速并行处理优势。

图二Cyclone®V SoC FPGA整体架构图

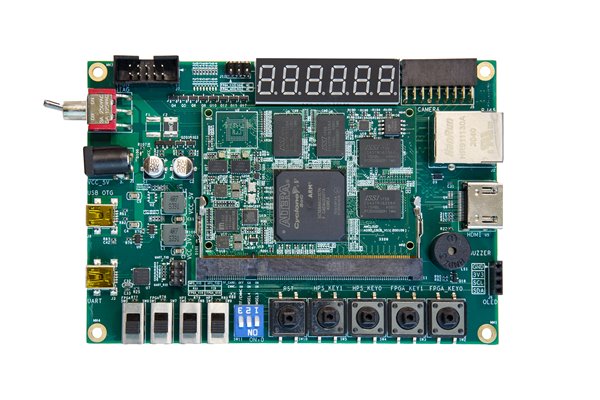

此外,搭载Cyclone®V SoC FPGA芯片的硬件平台是由重庆海云捷迅科技有限公司自主研发的AIGO_C5MB Development Kit。平台采用核心板加扩展板的方式,方便用户对核心板的二次开发利用。核心板以Cyclone®V SoC芯片为核心,芯片不仅仅将双核Cortex-A9嵌入式内核与FPGA可编程逻辑相结合,还具有与高性能、低功耗处理器系统相结合的强大的可重新配置能力。Intel SoC集成了一个基于ARM的HPS,该系统由处理器、外设和内存接口组成,并通过一个高带宽的互联网络与FPGA结构进行无缝连接。另外,核心板上搭载高速芯片、千兆以太网PHY以及USB2.0 PHY。其扩展板则是为用户提供了丰富的外设接口。可以满足用户各种高速数据交换、数据存储、视频传输处理以及工业控制的需求。为高速数据传输和交换、数据处理的前期验证和后期应用提供了可能,也为高校的开发教学、工程师的深度开发等提供了适用性。

图03 AIGO_C5MB Development Kit实物图

技术路线

成果实现的技术手段主要为将果壳NutShell RISC-V处理器架构与Cyclone®V SoC FPGA的“FPGA(PL)+ARM(PS)”架构进行适配,并在Intel自有的硬件开发平台Quartus Prime中进行硬件平台搭建以及相关代码编写。

项目成果

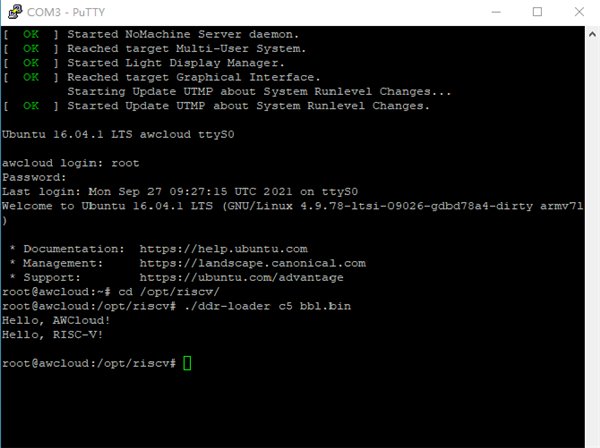

完成架构适配、硬件平台搭建以及相关代码编写后,可正确控制串口外设打印如下信息。

图四成果展示图

感谢中国科学院计算技术研究所和香山技术团队的大力支持!

重庆海云捷迅科技有限公司将持续和中国科学院计算技术研究所以及香山技术团队展开合作,实现与高性能开源RISC-V处理器“香山”的对接以及相关功能的应用。重庆海云捷迅科技有限公司将持续在RISC-V领域发挥重要作用以及在自主可控之路中砥砺前行。

作者简介

彭诗翰,重庆海云捷迅科技有限公司-FPGA工程师。美国佛蒙特大学电子电气工程及数学双学士学位、美国东北大学电子电气与电脑工程硕士学位。具备出色的项目管理能力,且熟知FPGA异构计算、人工智能等相关技术,精通Arduino、Matlab的实操运用。