芯片设计全流程(Full Chip Design Flow)是一个高度复杂、系统性极强的工程过程,涉及多个学科的知识,包括数字电路、模拟电路、微电子工艺、EDA 工具、计算机体系结构等。每一步都在实现一个完全可运行芯片的目标中起着关键作用。本文概述了芯片设计流程的各个阶段,以及它们在构建高效芯片中的作用。这些阶段包括:系统规格定义、架构设计、功能设计、逻辑设计、电路设计、物理设计验证以及制造。

在任何一个新的开发项目开始时,首要任务是确定要设计的器件/产品类型,例如集成电路(IC)、专用集成电路(ASIC)、现场可编程门阵列(FPGA)、系统级芯片(SoC)等。

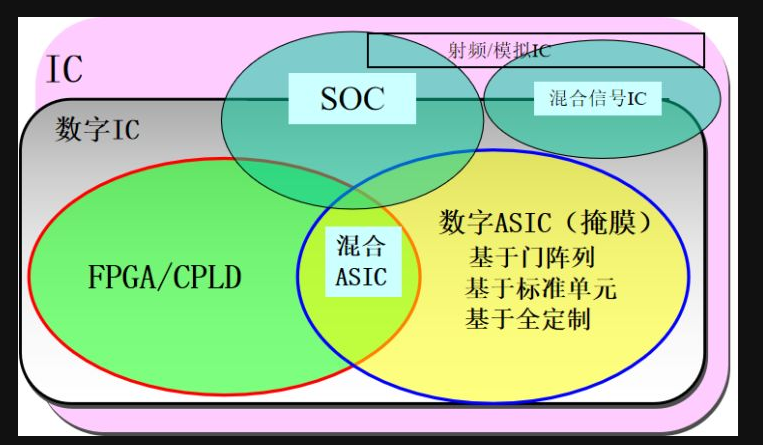

如上图所示,IC设计可以粗分为数字IC设计和射频/模拟IC设计;数字IC设计又可分为ASIC设计和FPGA/CPLD设计;此外还有一部分IC设计采用数模混合设计,如:SOC设计和数模混合信号IC设计。

如上图所示,IC设计可以粗分为数字IC设计和射频/模拟IC设计;数字IC设计又可分为ASIC设计和FPGA/CPLD设计;此外还有一部分IC设计采用数模混合设计,如:SOC设计和数模混合信号IC设计。

如果目标是设计一个既小巧又足够强大、适用于高速应用(如电信或网络设备)的芯片,最好的选择可能是 ASIC(Application-Specific Integrated Circuit,应用专用集成电路);而如果目标是设计一种更加灵活、能够以较小的资源开销完成多任务处理的芯片,那么 FPGA(Field-Programmable Gate Array,现场可编程门阵列)可能是更好的选择。一旦确定了芯片类型,便可以进一步明确其规格参数。

关于数字IC中的ASIC与FPGA/CPLD的区别:

ASIC(Application Specific Integrated Circuit,专用集成电路):需制作掩模,设计时间长,硬件不能升级;芯片面积小,性能可以得到较好的优化;适合芯片需求量大的场合:片量用于平摊昂贵的光罩掩模制版费,降低单片生产成本。

FPGA/CPLD(Field Programmable Gate Array,现场可编程门阵列 / Complex Programmable Logic Device,复杂可编程逻辑器件):不需要后端设计/制作掩模,可编程;开发门槛较低,设计时间较短,可方便和快速地升级优化硬件;芯片面积大,性能不够优化 ;适合芯片需求量小的场合:不用支付昂贵的光罩掩模制版费。作为数字ASIC设计流程中的必要步骤:ASIC设计中前端设计的FPGA原型验证(HDL功能验证)。

模拟/射频IC:处理模拟信号,规模远不如数字IC,放大器( RF放大器、中放、运放、功放);比较器;振荡器;混频器;模拟PLL;稳压稳流源等

数模混合信号IC: ADC、DAC;某些Driver;电源管理;等等

SOC:System on Chip(系统集成电路,片上系统)

芯片设计的概念

芯片是一种微小的电子器件,其被编程用于执行特定功能。这些器件被广泛应用于各类场景,如计算机、手机等。超大规模集成电路(VLSI)技术彻底革新了电子行业,使设计人员能够在一颗芯片上集成数百万乃至数十亿个晶体管。这推动了强大处理器、存储器件及其他先进电子系统的发展。

芯片的设计技术会依据其应用需求而有所不同。下面我们来详细了解整个芯片设计流程。

以下是目前主流数字集成电路(尤其是 SoC,System on Chip)的详细设计流程,按阶段划分:

一、规格定义阶段(Specification Definition)

芯片设计流程的第一步是定义芯片的需求与规格。这包括确定产品的功能、使用方式,以及需要满足的性能指标。一旦这些需求被明确定义,它们就可以作为输入用于架构设计与芯片布局规划。

在明确需求之后,下一步是设计能够满足这些要求的系统架构,同时还需考虑成本、功耗等因素。在芯片设计的初期阶段,设计者需要就架构做出关键决策,例如在 RISC(精简指令集计算机)与 CISC(复杂指令集计算机)之间做出选择,确定所需的算术逻辑单元(ALU)的数量,决定流水线的结构与数量,选择缓存的大小等等。这些决策构成了整个设计流程的基础,因此设计人员必须对每一方面进行仔细评估,充分考虑其对芯片整体效率与性能的影响。这些选择均应基于芯片的目标用途与事先定义的技术规格,最终目标是打造一个高效、性能强且低功耗、低成本的设计。

1.1 系统需求分析

1.2 架构设计(Architecture Design)

- 确定 CPU/GPU/AI加速器/ISP 等 IP 模块的配置

- 确定总线架构(如 AXI、AHB)、缓存层级(L1/L2/L3)

- 功耗预算(Power Budget)、时钟频率(Clock Tree Planning)

- 通信接口(PCIe、USB、DDR、MIPI 等)

- 安全性与可测试性(Secure Boot, DFT)需求

在完成架构设计阶段后,设计者会制定一份微架构规格文档(MAS,Micro-Architectural Specification),这是对芯片架构的书面描述。该规格文档使设计人员能够准确预测设计的性能表现、功耗以及芯片尺寸(Die Size)。通过制定全面的 MAS,可以确保芯片设计符合在初期定义阶段设定的需求和规格。MAS 的详尽程度至关重要,它有助于避免后期出现设计错误,并确保芯片在性能标准与时间进度方面的达成。这一阶段可能还涉及在不同类型的处理器或 FPGA 之间进行选择。

二、前端设计阶段(Front-End Design)

在完成微架构规格(MAS)之后,下一步是功能设计阶段。在此阶段,设计者会使用硬件描述语言(HDL),如 Verilog 或 VHDL,对芯片的各个模块进行编码。这些模块可能包括算术逻辑单元(ALU)、寄存器堆、控制逻辑、总线接口、缓存控制器等。每个模块都应符合架构和微架构阶段所定义的行为和接口规范。

设计者通常会采用模块化开发方式,使得系统更易于调试、验证和后续集成。在这个阶段,设计团队还需要确保各模块之间的接口逻辑清晰、信号定义一致,同时考虑功耗管理、时钟域划分和复位策略等关键设计因素。

功能设计的核心目标是确保 RTL 级别(寄存器传输级)实现符合架构定义的行为规范,为后续的验证与逻辑综合打下基础。完成 RTL 编码后,设计人员需要验证其功能是否正确。这一阶段至关重要,通常被认为是整个芯片设计周期中最耗时的部分之一。

主要方法包括:

-

仿真(Simulation):通过构建测试平台(Testbench),对 RTL 设计进行输入/输出验证;

-

覆盖率分析(Coverage Analysis):分析测试用例是否覆盖了所有状态、分支、路径等;

-

形式验证(Formal Verification):通过数学方法验证某些性质是否在设计中恒成立;

-

仿真框架:如 SystemVerilog + UVM(通用验证方法学)用于构建可复用验证平台。

目的是找出设计中的逻辑错误或潜在 Bug,并在逻辑综合之前将其修复。

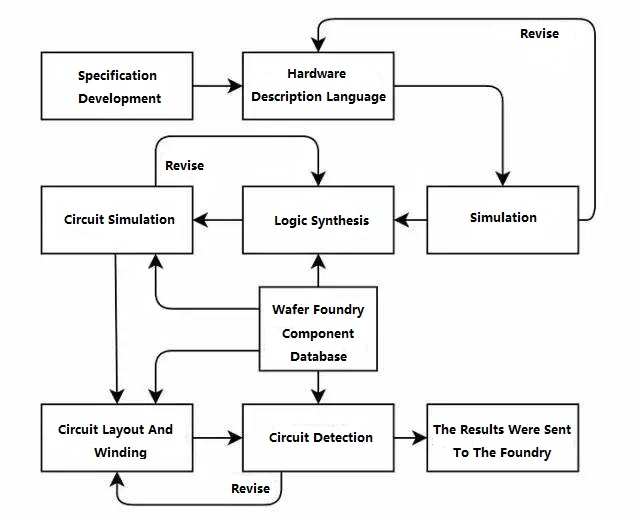

在功能验证通过后,下一步是将 RTL 描述转换为门级表示(Gate-Level Netlist),这一过程称为逻辑综合。

逻辑综合流程:

-

读取 RTL(Verilog/VHDL/SystemVerilog)

-

加载约束文件(SDC – Synopsys Design Constraints)

-

包含时钟频率、IO 延迟、功耗限制等信息

-

-

生成网表文件(Netlist),描述门电路级实现

在这一阶段,设计人员将与目标库(Standard Cell Library)配合,根据时序、功耗、面积等目标,选择适合的逻辑门来实现 RTL 行为。

此外,还会进行:

-

时序分析(Static Timing Analysis,STA):确保设计在所有路径上满足 setup/hold 要求;

-

功耗估算:初步估算动态功耗与静态功耗;

-

逻辑等价性检查(LEC):确保综合后的网表与原始 RTL 行为一致。

2.1 功能设计(RTL Design)

- 使用 HDL(Verilog/VHDL/SystemVerilog)编写模块级功能描述

- 多采用模块化设计,如 ALU、控制器、FIFO、DMA、Cache 等

- 软件与硬件协同设计(HW/SW Co-Design)

2.2 功能仿真(Functional Simulation)

- 使用 ModelSim、VCS、NC-Sim 等工具

- 编写 Testbench 验证模块功能

- 支持通用仿真环境(如 UVM)

2.3 形式验证(Formal Verification)

- 检查 RTL 设计的等价性、死锁、覆盖率等

- 使用工具:JasperGold、Formality 等

2.4 逻辑综合(Logic Synthesis)

- 使用 Synopsys Design Compiler、Cadence Genus 等工具

- 将 RTL 代码转换为门级网表(Gate-level Netlist)

- 目标库为标准单元库(Standard Cell Library)

- 进行约束设定(.sdc)如时钟约束、IO 时序、功耗控制

2.5 静态时序分析(Static Timing Analysis, STA)

- 使用 PrimeTime 等工具对网表进行时序分析

- 包括 Setup/Hold violations、路径延迟等

2.6 DFT 设计(Design for Testability)

三、后端设计阶段(Back-End Design / Physical Design)

在逻辑设计完成后,设计流程进入后端设计阶段,也称为物理设计(Physical Design)。该阶段的目标是将门级网表转化为实际的物理布局,并考虑信号、电源、时钟、面积等物理因素。芯片设计流程中的“后端设计”是将前端生成的 RTL(寄存器传输级)或门级网表,转换为可制造的物理版图(Layout)的全过程。它涉及一系列精密的步骤,最终目标是生成符合工艺规范的 GDSII 文件,用于流片生产。

主要步骤包括:

3.1. Floorplanning(芯片平面规划)

3.2. Placement(单元放置)

-

将综合得到的标准单元逻辑门放置在芯片布局中;

-

避免拥塞、提升局部连线效率。

3.3. 时钟树综合(Clock Tree Synthesis,CTS)

-

构建低偏斜、高容错的时钟树结构;

-

确保所有触发器获得稳定的时钟信号,减少时钟偏移(Clock Skew)。

3.4. Routing(布线)

-

完成所有信号线、电源线、时钟线的连通;

-

使用多层金属布线(通常 5~15 层);

-

进行信号完整性(SI)、串扰(Crosstalk)检查。

3.5. 时序收敛(Timing Closure)

-

修复时序违规路径(违反 setup/hold);

-

插入缓冲器、调整驱动强度、优化连线;

-

使用 ECO(Engineering Change Order)进行小范围逻辑修改。

物理验证(Physical Verification)

完成布局布线之后,必须执行一系列物理验证步骤,确保设计满足制造工艺规则:

3.6. DRC(设计规则检查)

-

确保线宽、间距、孔径、金属层等符合晶圆厂设计规则;

-

工具:Mentor Calibre DRC、Cadence Pegasus。

3.7. LVS(电路图与版图一致性检查)

-

检查物理版图是否与逻辑网表完全一致;

-

工具:Calibre LVS、StarRC。

3.8 ERC(电气规则检查)

-

检查非法连接、电压冲突、悬空节点等问题。

3.9. IR Drop / EM 检查

这些验证步骤确保芯片在实际制造后可以稳定运行。

四、签核与流片(Signoff and Tape-Out)

当芯片完成所有设计与验证流程后,进入最终“签核”阶段(Signoff),即准备将设计数据交付给晶圆厂制造:

4.1. 签核内容包括:

-

完整版图文件(GDSII / OASIS);

-

标准单元库文件(LIB、LEF);

-

工艺文件、时钟、时序与功耗报告;

-

形式验证报告、仿真波形、功能验证文档。

4.2 流片(Tape-Out):

五、制造、封装与测试(Fabrication, Packaging, and Testing)

5.1. 晶圆制造(Wafer Fabrication)

-

在洁净室中进行光刻、扩散、刻蚀、离子注入等工艺;

-

形成多个芯片的晶圆(Die)。

5.2. 切割与封装(Dicing & Packaging)

-

将晶圆切割成独立芯片;

-

封装成不同封装形式:BGA、WLCSP、QFN、Flip-Chip;

-

加装金属引脚、热封装、连接基板。

5.3. 测试(Testing)

-

晶圆测试(Wafer Sort):使用探针卡检测裸片功能;

-

使用自动测试设备(ATE)进行量产级测试;

-

筛选出良品,统计良率。

六、量产与维护(Mass Production & Maintenance)

对量产数据进行分析(良率分析、失效分析、环境测试),若发现设计缺陷,可能进行 Metal ECO 或重新流片;软件团队开展驱动开发与系统验证;设计团队提供 silicon debug、功能更新支持等。

6.1 良率分析(Yield Analysis)

- 分析失效原因(DFM)、测试覆盖率

6.2 产品验证与客户交付(Validation & Shipment)

- 软件驱动验证、系统集成测试

- 客户验证(Customer Acceptance)

6.3 芯片维护(ECO、Patch)

- 若发现逻辑Bug,可通过金属层 ECO 或后期 Mask Fix 修复

七、常用工具与公司(EDA/Foundry)

主流 EDA 工具商:

- Synopsys:DC、PrimeTime、IC Compiler、HSPICE

- Cadence:Genus、Innovus、Voltus、Spectre

- Siemens EDA (原 Mentor):Calibre、Tessent

- Ansys:RedHawk、Totem(电源完整性)

晶圆代工厂(Foundry):

总结:整个芯片设计流程简图

|

1 2 3 4 5 6 7 8 |

1. 系统规格与架构设计(System Specification & Architecture) 2. 功能设计与验证(RTL Design & Functional Verification) 3. 逻辑综合与静态时序分析(Logic Synthesis & STA) 4. 物理设计(布局布线,CTS,功耗分析) 5. 物理验证(DRC / LVS / ERC / IR Drop) 6. Tape-Out(流片交付) 7. 晶圆制造与封装测试 8. 量产、良率提升与维护 |

芯片设计全流程图(Chip Design Full Flow Diagram)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 |

┌────────────────────────────────────────────────────────────┐ │ 1. 系统需求与规格定义 │ │ System Specification & Requirement Definition │ │ • 产品功能目标(Functionality) │ │ • 性能/功耗/成本约束(Performance, Power, Cost) │ │ • 工艺选择:CMOS 工艺节点(如 7nm, 28nm 等) │ │ • 芯片类型选择(ASIC / FPGA / SoC) │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 2. 架构设计与微架构设计 │ │ Architecture & Micro-Architecture Design │ │ • 指令集结构(ISA: RISC / CISC) │ │ • 模块划分:ALU, Cache, Bus, Pipeline 等 │ │ • 微架构规范文档(Micro-Architecture Spec, MAS) │ │ • 接口定义(Interfaces, Protocols) │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 3. RTL 功能设计 │ │ RTL Functional Design (Verilog/VHDL) │ │ • 模块级 HDL 编码 │ │ • 时钟域划分与复位策略 │ │ • 多模块集成与接口实现 │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 4. 功能验证 │ │ Functional Verification │ │ • 仿真(Simulation) │ │ • UVM 测试平台与 Testbench 构建 │ │ • 覆盖率分析(Coverage) │ │ • 形式验证(Formal Verification) │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 5. 逻辑综合与时序分析 │ │ Logic Synthesis & Static Timing Analysis │ │ • 综合工具:Synopsys DC / Cadence Genus │ │ • SDC 约束文件(时钟、IO、时序要求) │ │ • 网表输出(Gate-Level Netlist) │ │ • 逻辑等价性检查(LEC) │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 6. 物理设计 │ │ Physical Design │ │ • Floorplanning(宏单元布局) │ │ • Placement(标准单元放置) │ │ • CTS(Clock Tree Synthesis) │ │ • Routing(信号布线) │ │ • 功耗分析、拥塞分析、时序收敛 │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 7. 物理验证(签核) │ │ Physical Verification (Signoff Checks) │ │ • DRC(设计规则检查) │ │ • LVS(版图与电路一致性检查) │ │ • ERC(电气规则检查) │ │ • IR Drop / EM 分析 │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 8. Tape-Out │ │ Final Signoff & GDSII 交付给晶圆厂 │ │ • GDSII / OASIS 数据 │ │ • 时序 / 功耗 / 报告文档 │ │ • IP、标准单元库文档 │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 9. 晶圆制造与流片 │ │ Wafer Fabrication (由晶圆厂完成) │ │ • 光刻、离子注入、金属化等步骤 │ │ • 工艺平台:TSMC / SMIC / Intel / GlobalFoundries 等 │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 10. 封装与测试 │ │ Packaging & Final Testing │ │ • 封装类型:BGA, QFN, WLCSP, Flip-Chip 等 │ │ • Wafer Sort(晶圆探针测试) │ │ • Final Test(功能/电压/温度测试) │ │ • ATE(自动测试设备) │ └────────────────────────────────────────────────────────────┘ ↓ ┌────────────────────────────────────────────────────────────┐ │ 11. 量产与维护支持 │ │ Production & Post-Silicon Support │ │ • 良率分析 / 失效分析 │ │ • Silicon Debug / ECO │ │ • 软件支持与驱动开发 │ └────────────────────────────────────────────────────────────┘ |