如果说 CPU 是“大脑”,

那么 Register File 就是它的“短期记忆”。

在上一篇里,我们讲了 RV32I 是什么。但 CPU 真正“工作”的关键,不是指令本身,而是:

👉 数据放在哪里?怎么被快速读取?

答案就是:Register File(寄存器堆)

🔍 一、什么是 Register File?

Register File 是 CPU 内部的一组超高速存储单元。

👉 简单理解:

它是一小块“极快的存储”,专门给 CPU 自己用

🧩 在 RV32I 里:

- 一共有 32 个寄存器

- 命名为:

x0 ~ x31 - 每个寄存器:32位

⚠️ 特殊规则(非常重要)

|

1 2 |

x0 永远等于 0(不能被修改) |

👉 这点在硬件设计中必须强制保证

⚙️ 二、为什么 CPU 一定需要 Register File?

很多初学者会问:

👉 “为什么不用内存(RAM)就好了?”

答案是:速度差太多

🐢 内存 vs ⚡ 寄存器

| 类型 | 速度 | 用途 |

|---|---|---|

| Register | 极快 | CPU计算 |

| RAM | 中等 | 存数据 |

| Disk | 很慢 | 存文件 |

👉 CPU 每个周期都要运算:

如果每次都访问 RAM:

❌ 太慢

❌ 性能崩溃

👉 所以:

寄存器 = CPU的“随手可用数据”

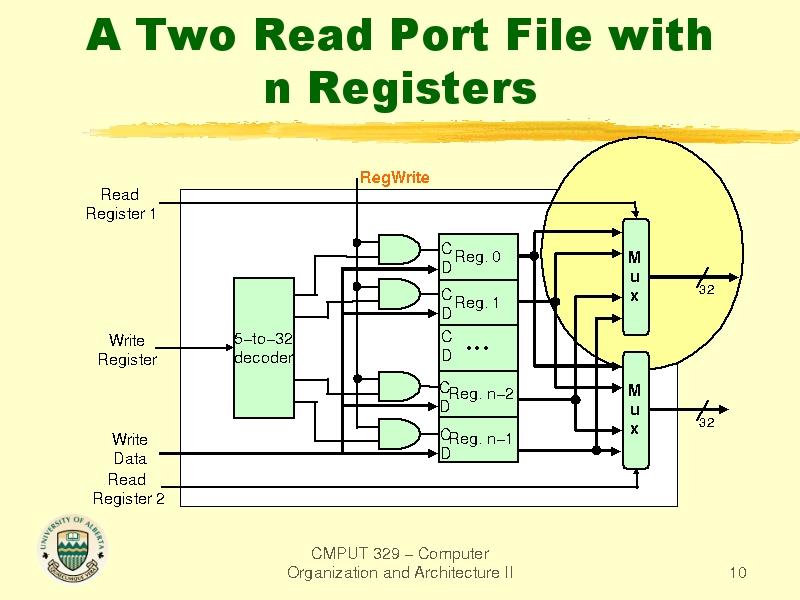

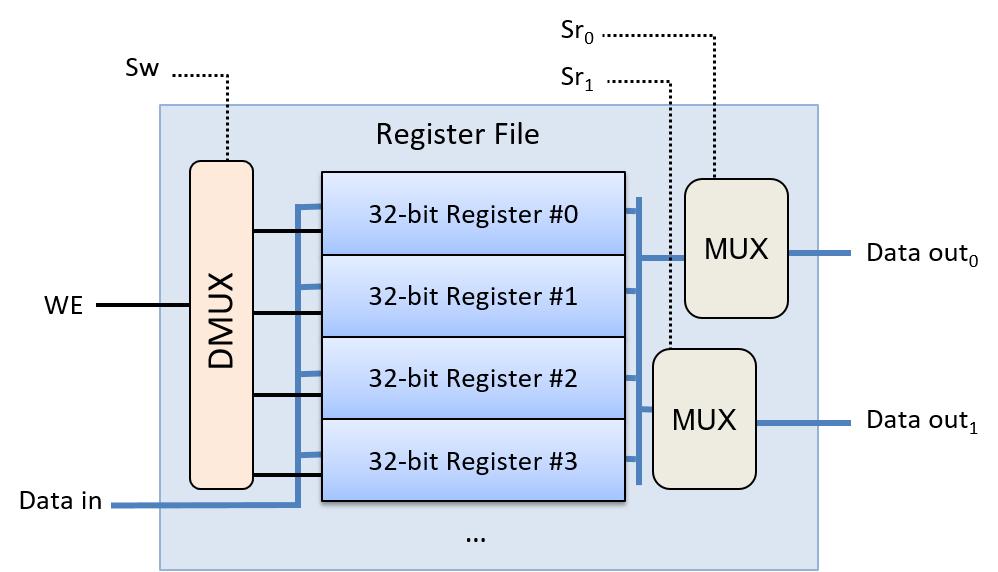

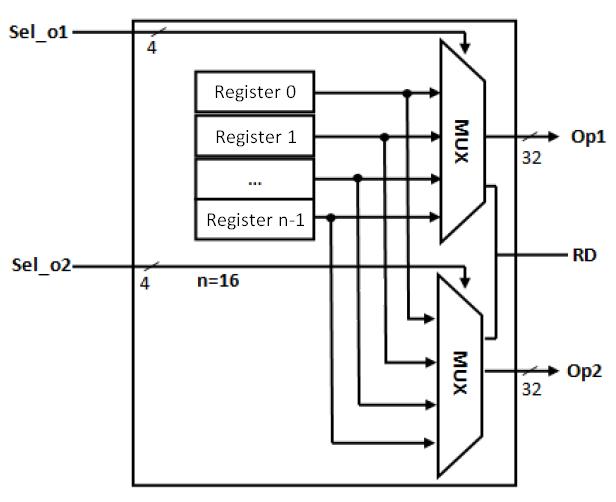

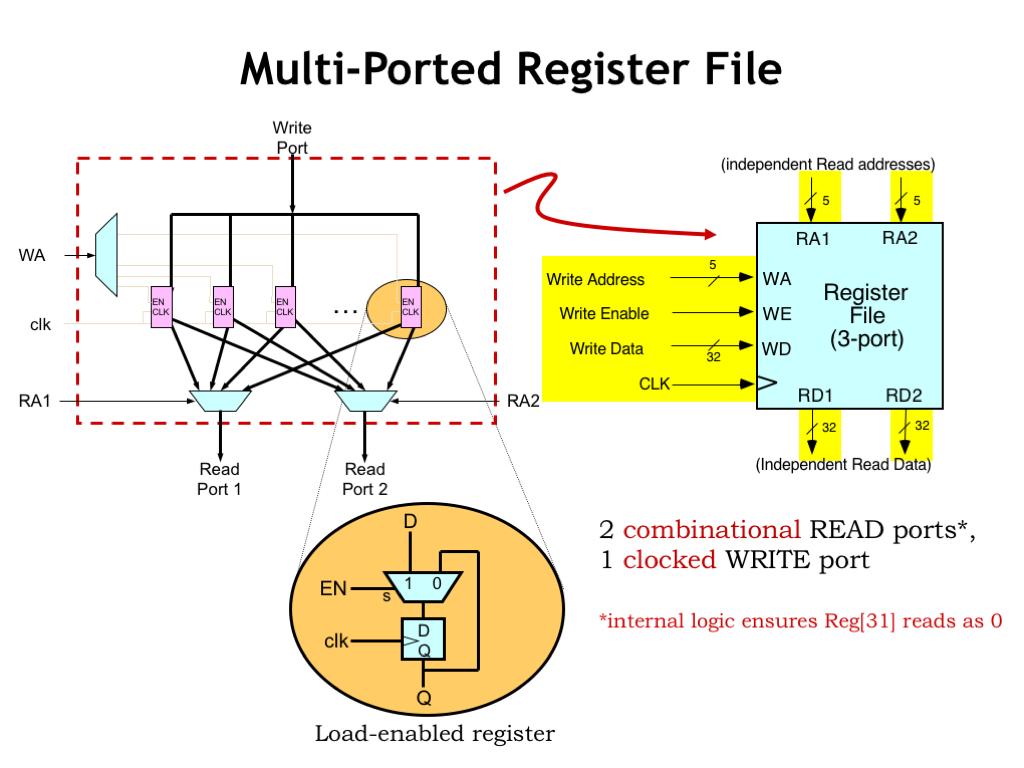

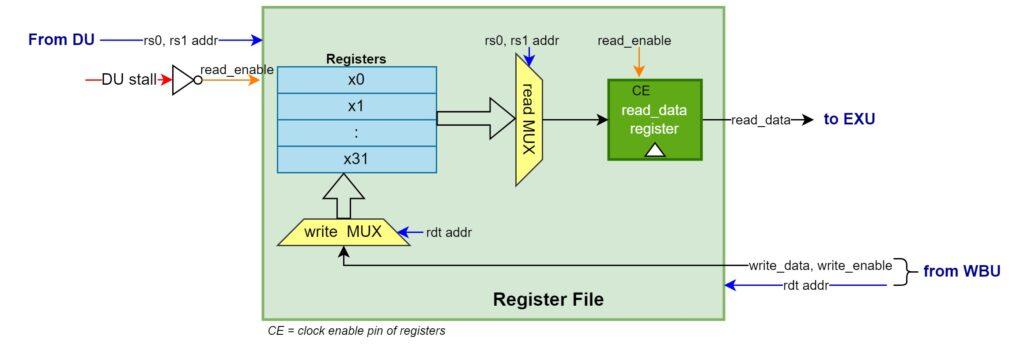

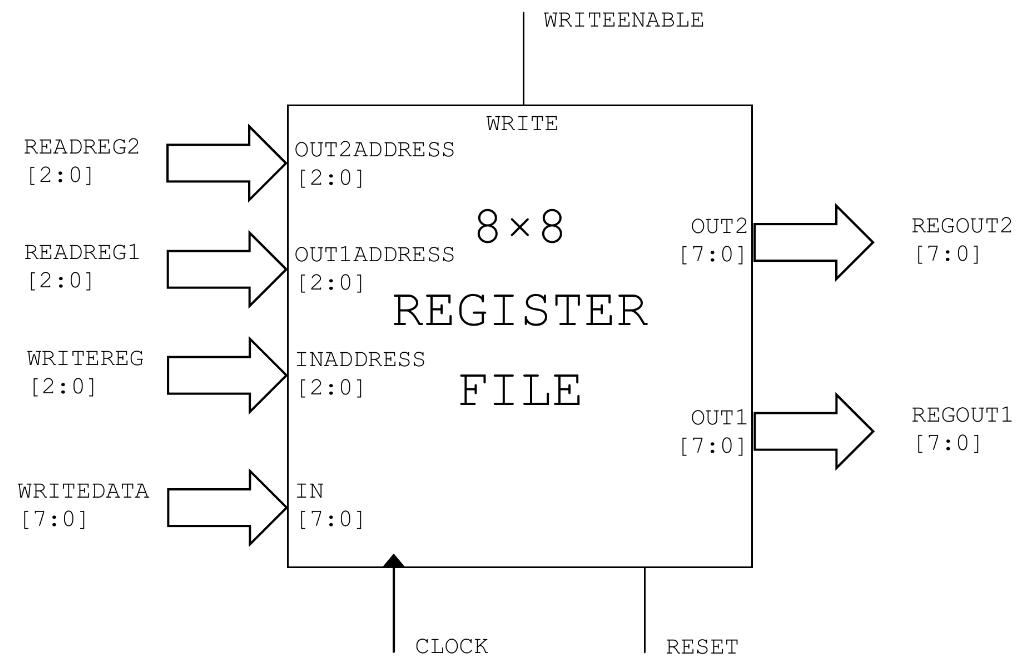

🏗️ 三、Register File 的结构

一个典型的 Register File 包含:

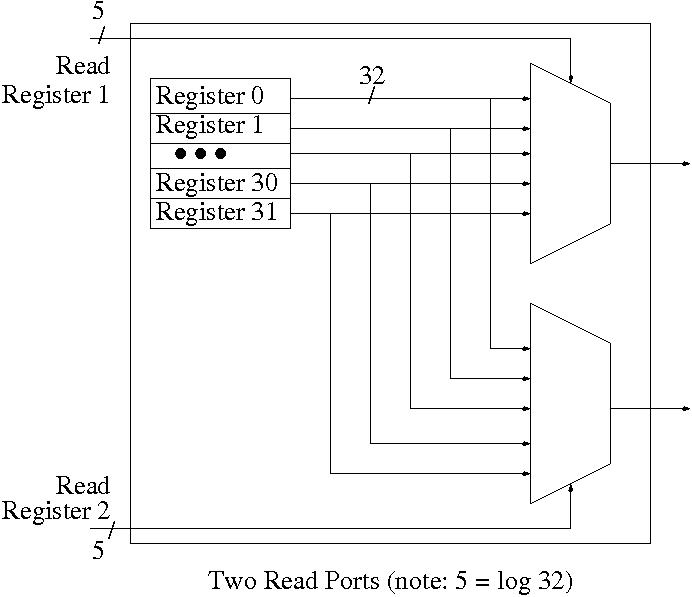

🟢 2个读端口(Read Ports)

👉 同时读取两个寄存器

例如:

|

1 2 |

ADD x3, x1, x2 |

需要读取:

- x1

- x2

🔵 1个写端口(Write Port)

👉 把结果写回寄存器

上面的例子:

- 写入 x3

👉 总结结构:

|

1 2 |

2 Read + 1 Write |

这是 CPU 的经典设计

🔄 四、一次完整操作过程

以这条指令为例:

|

1 2 |

ADD x3, x1, x2 |

执行流程:

1️⃣ 从寄存器堆读取 x1

2️⃣ 从寄存器堆读取 x2

3️⃣ ALU 相加

4️⃣ 结果写入 x3

👉 关键点:

寄存器是“数据流的起点和终点”

🧠 五、从软件思维 → 硬件思维

很多人写代码时会这样想:

|

1 2 |

c = a + b; |

但在 CPU 里,真正发生的是:

|

1 2 3 4 |

x1 → ALU x2 → ALU 结果 → x3 |

👉 没有“变量”,只有寄存器

⚡ 六、Verilog 实现(最小版本)

下面是一个最简 Register File 示例:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

module regfile ( input clk, input we, // write enable input [4:0] rs1, rs2, rd, // register index input [31:0] wd, // write data output [31:0] rd1, rd2 // read data ); reg [31:0] regs [31:0]; // read (combinational) assign rd1 = (rs1 == 0) ? 0 : regs[rs1]; assign rd2 = (rs2 == 0) ? 0 : regs[rs2]; // write (sequential) always @(posedge clk) begin if (we && rd != 0) regs[rd] <= wd; end endmodule |

🔥 关键设计点:

x0强制为 0- 读是组合逻辑(立即输出)

- 写是时钟触发

🚨 七、常见错误(新手必踩)

❌ 忘记 x0 = 0

👉 会导致所有计算错误

❌ 读写时序搞错

👉 会出现数据不一致

❌ 写入冲突

👉 多写口设计错误

💡 八、为什么它是 CPU 最关键模块之一?

因为:

👉 所有计算都依赖它

- ALU 输入来自它

- 结果写回它

- 指令围绕它展开

👉 没有 Register File:

❌ CPU 无法计算

❌ 指令无法执行

🚀 九、下一步你将做什么?

下一篇我们进入核心:

👉 《ALU 是什么?CPU是如何真正“计算”的》

你将学会:

- 如何实现 ADD / SUB

- 如何设计 ALU

- 如何连接寄存器

📌 总结

- Register File 是 CPU 的高速数据存储

- RV32I 有 32 个寄存器

- 结构是:2读 + 1写

- 所有计算都围绕它展开

👉 一句话:

寄存器不是存数据的地方,而是“计算发生的地方”