🚀 Cache:为什么 CPU 再快也要等内存

但性能还是不够。

问题不在 CPU。

👉 在内存。

🔍 一、真正的瓶颈:Memory Wall

很多人以为:

|

1 2 |

性能 = CPU速度 |

但现实是:

👉 CPU 很快,内存很慢

📊 大致对比:

| 组件 | 延迟 |

|---|---|

| 寄存器 | ~1 cycle |

| L1 Cache | ~4 cycles |

| L2 Cache | ~10 cycles |

| RAM | ~100+ cycles |

👉 CPU 可以在 1 个周期算完

👉 但可能要等 100个周期 才拿到数据

👉 这就是:

Memory Wall(内存墙)

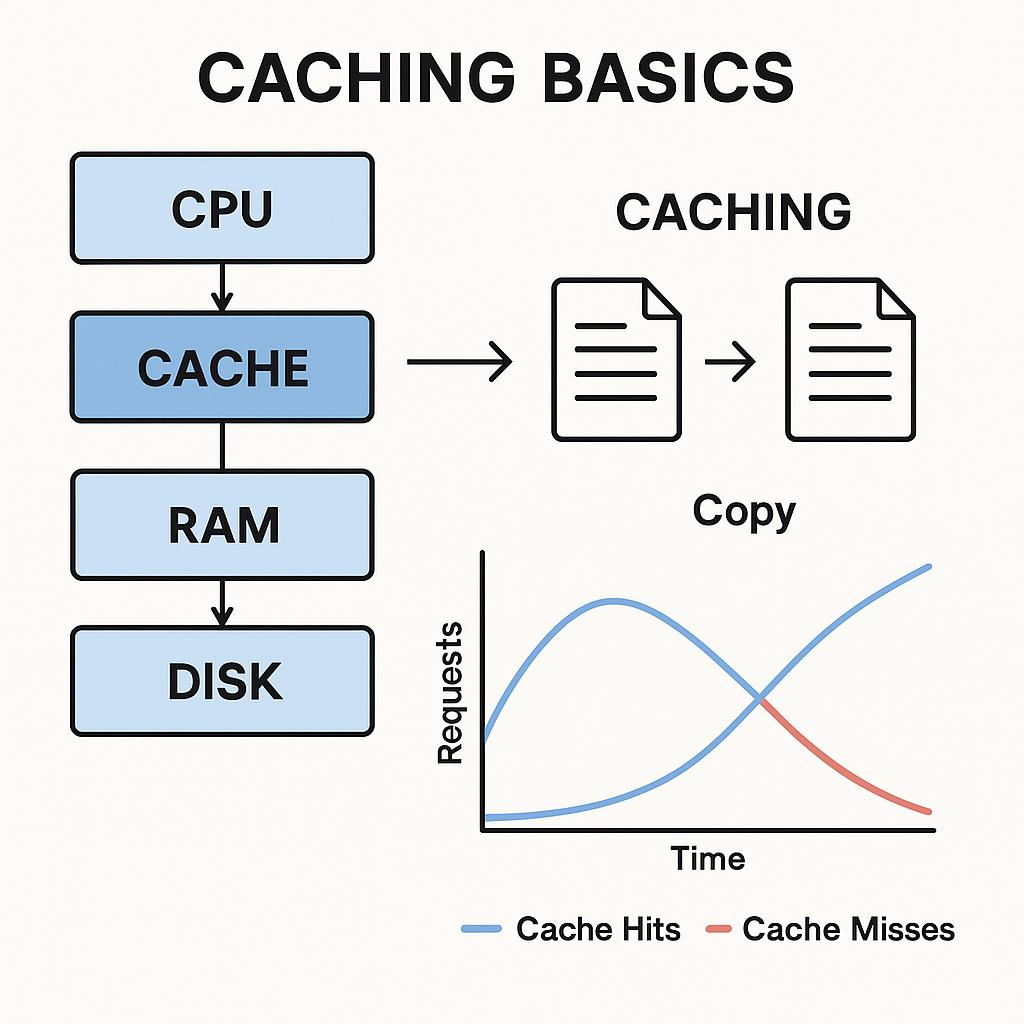

🧠 二、Cache 是什么?

Cache(缓存)本质是:

一个更小、更快的“中间存储”

👉 放在 CPU 和内存之间:

|

1 2 |

CPU ↔ Cache ↔ RAM |

👉 思想很简单:

把“常用数据”放在更近的地方

🧩 三、为什么 Cache 有效?

因为程序有一个非常重要的特点:

🔁 局部性(Locality)

1️⃣ 时间局部性

👉 用过的数据,很快还会再用

2️⃣ 空间局部性

👉 用了某个地址,附近的数据也可能用

👉 所以:

缓存最近用过的数据 = 极高命中率

⚙️ 四、Cache 是怎么工作的?

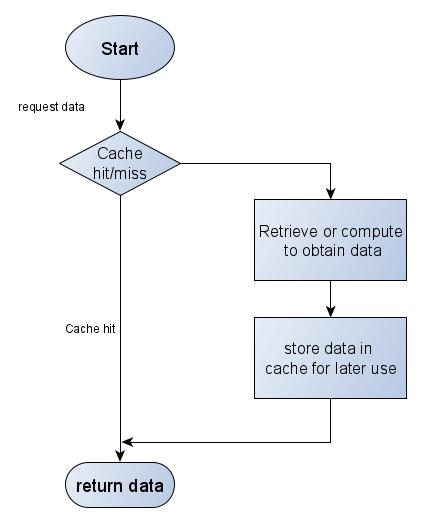

当 CPU 访问数据:

情况1:Cache Hit(命中)

|

1 2 |

数据在 Cache 中 |

👉 直接返回

👉 很快

情况2:Cache Miss(未命中)

|

1 2 |

Cache 没有 |

👉 去 RAM 取

👉 很慢

👉 同时把数据放进 Cache

👉 核心:

尽量减少 miss

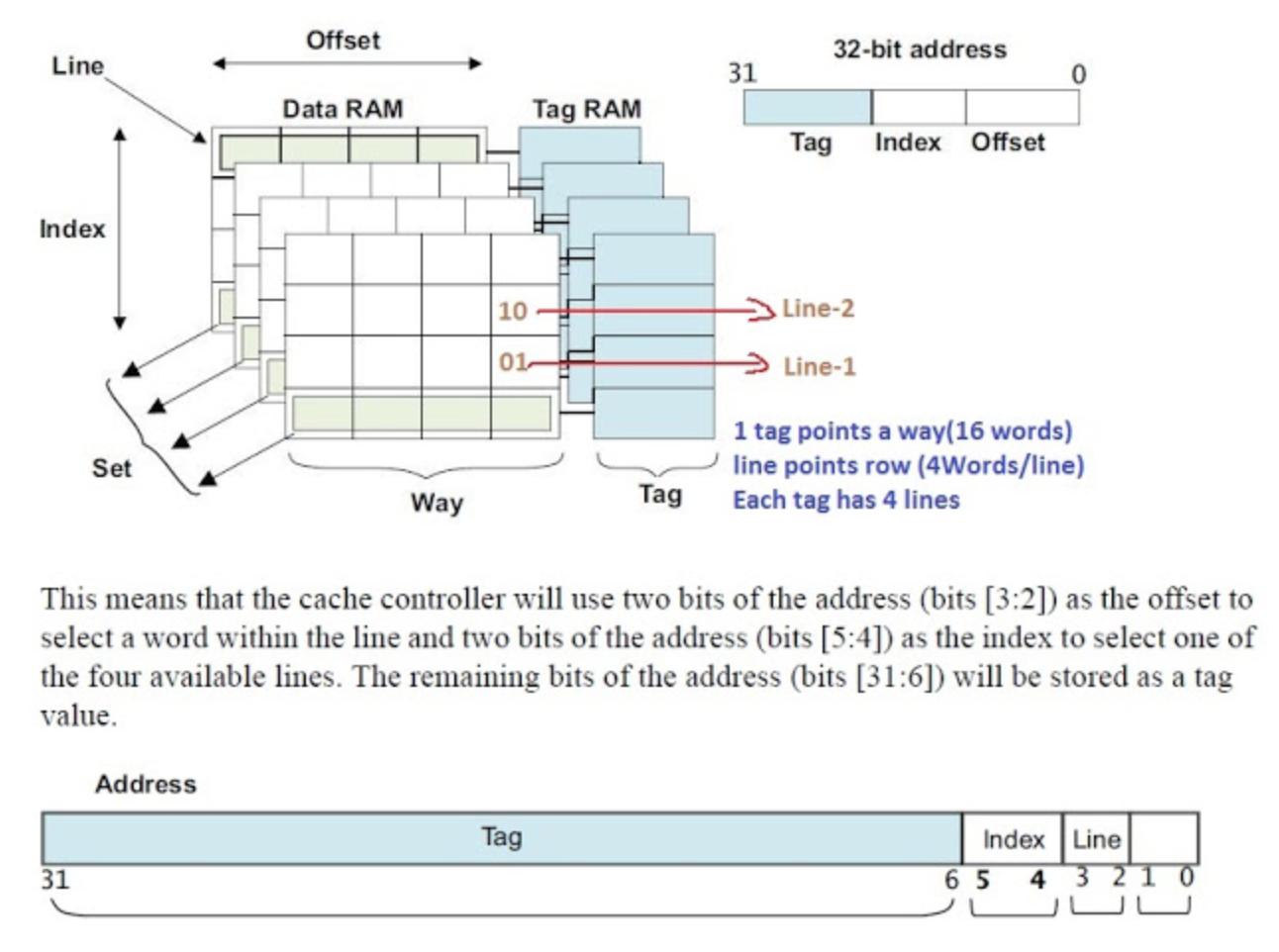

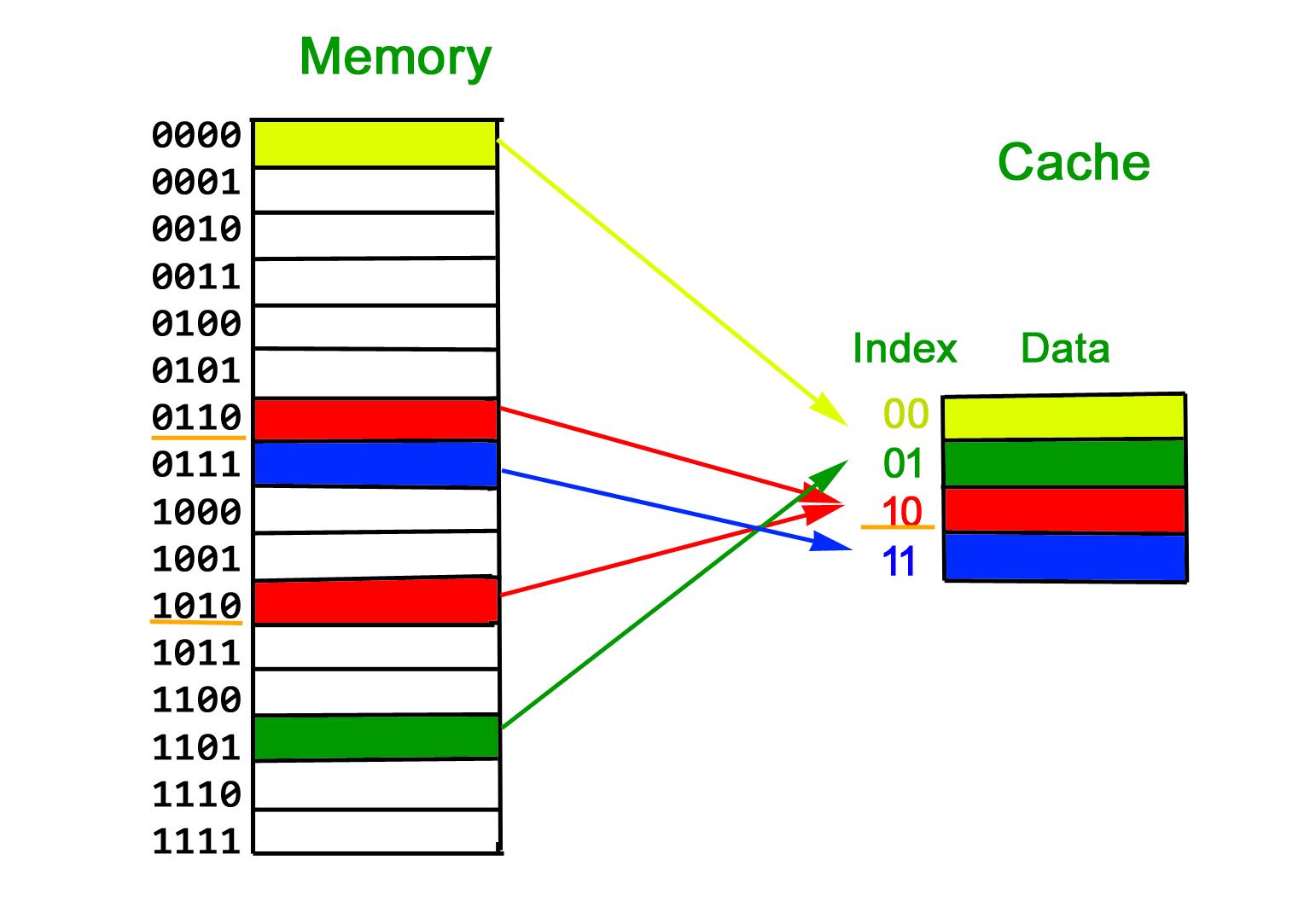

🏗️ 五、Cache 的基本结构

一个 Cache 通常包含:

- Data(数据)

- Tag(地址标签)

- Valid bit(是否有效)

👉 CPU 查 Cache 时:

1️⃣ 根据地址找到位置

2️⃣ 比较 Tag

3️⃣ 判断是否命中

🔥 六、最简单的 Cache:Direct-Mapped

👉 每个内存地址只能放在一个位置

优点:

- 简单

- 快

缺点:

- 冲突多(容易 miss)

🔄 七、更高级:Set-Associative

👉 一个地址可以放多个位置

优点:

- 减少冲突

缺点:

- 更复杂

👉 这是现实 CPU 常用方案

⚠️ 八、为什么 Cache 仍然不完美?

即使有 Cache,也会:

❌ Conflict Miss

不同数据映射到同一位置

❌ Capacity Miss

Cache 太小

❌ Cold Miss

第一次访问

👉 所以:

Cache 是优化,不是解决方案

🧠 九、最重要的认知

👉 CPU 的速度,不取决于它算得多快

👉 而取决于:

|

1 2 |

数据到达它有多快 |

👉 所以现代 CPU:

- ALU 很快

- Pipeline 很深

👉 但真正决定性能的是:

👉 Cache 命中率

⚡ 十、和你之前内容的关系

你已经学了:

- Register File

- ALU

- Pipeline

👉 现在你看到:

👉 数据来源才是关键

👉 CPU 可以:

👉 不停计算

👉 但如果数据不在:

👉 它只能等

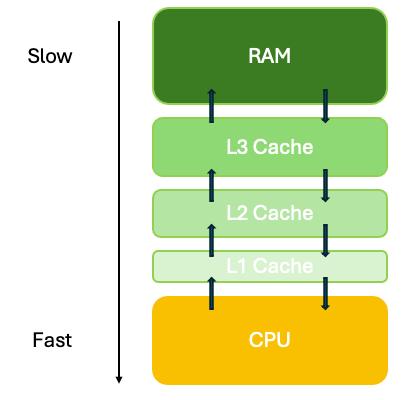

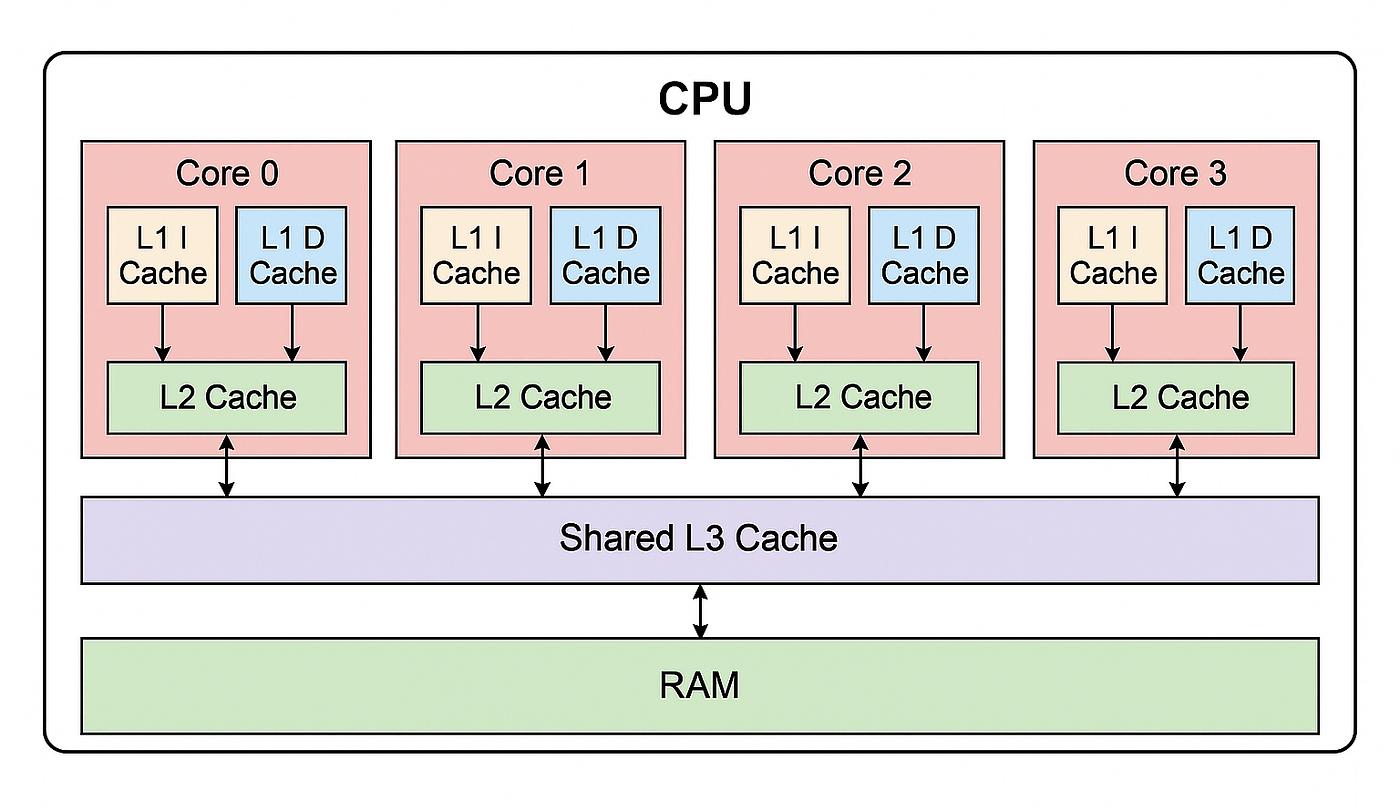

🚀 十一、现实中的 CPU

现代 CPU 有多级缓存:

|

1 2 |

L1 → L2 → L3 → RAM |

👉 越靠近 CPU:

- 越快

- 越小

👉 越远:

- 越慢

- 越大

👉 这是典型的:

速度 vs 容量 tradeoff

📌 十二、总结

- CPU 很快,但内存很慢

- Cache 是中间层,减少访问延迟

- 性能取决于命中率

- 局部性是核心原理

👉 一句话:

CPU 不怕计算慢,它怕等数据

🚀 下一篇

👉 《从 CPU 到系统:为什么性能不是单点问题》

你将看到:

- CPU + 内存 + IO 的关系

- 为什么优化一处不够

- 系统级性能思维