🧠 ALU 是什么?CPU 是如何真正“计算”的(附完整 Verilog)

如果说 Register File 是“数据来源”,

那么 ALU 就是——计算发生的地方

在 CPU 里,所有计算,本质都经过一个模块:

👉 ALU(Arithmetic Logic Unit)

🔍 一、什么是 ALU?

ALU = 算术逻辑单元

👉 它的作用很简单:

输入两个数据 → 执行操作 → 输出结果

🧩 在 RV32I 中,ALU 负责:

- 加法(ADD / ADDI)

- 减法(SUB)

- 逻辑(AND / OR / XOR)

- 比较(SLT / SLTU)

- 位移(SLL / SRL)

👉 所有指令,最终都会变成:

|

1 2 3 4 |

A → ALU B → ALU Result ← ALU |

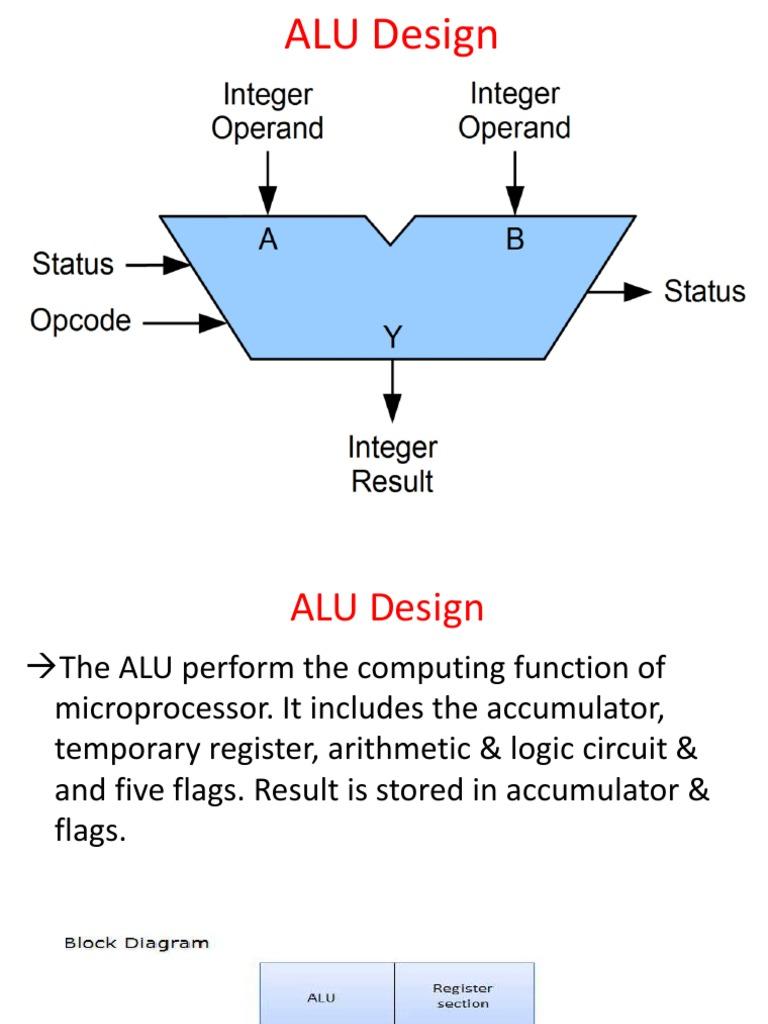

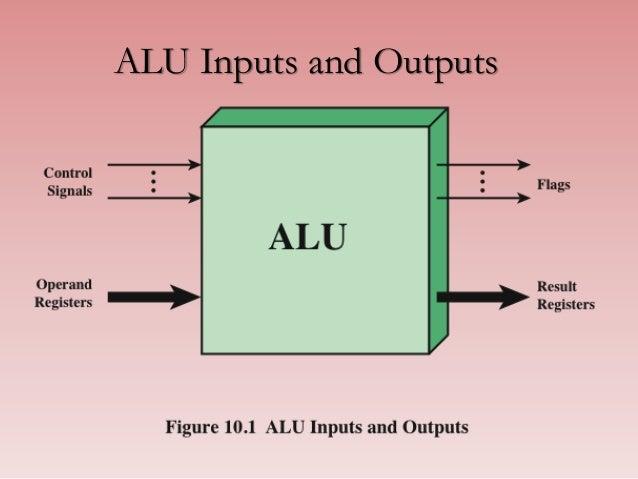

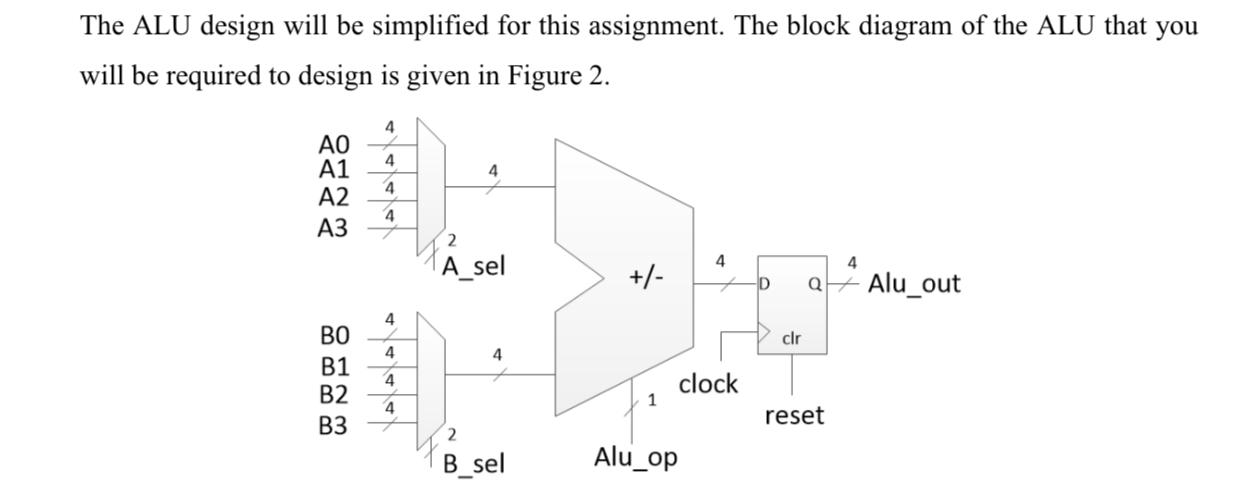

⚙️ 二、ALU 的基本结构

一个最小 ALU 包含:

- 输入 A(32-bit)

- 输入 B(32-bit)

- 控制信号(决定做什么运算)

- 输出 Result(32-bit)

👉 核心就是:

|

1 2 |

Result = f(A, B, Control) |

🔄 三、ALU 是如何工作的?

例如:

|

1 2 |

ADD x3, x1, x2 |

执行流程:

1️⃣ 从寄存器读取 x1 → A

2️⃣ 从寄存器读取 x2 → B

3️⃣ 控制信号 = ADD

4️⃣ ALU 输出 A + B

5️⃣ 写回 x3

👉 所有复杂程序,最终都归结为这些操作

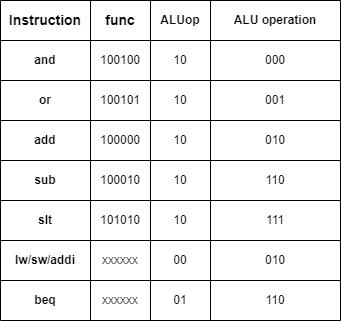

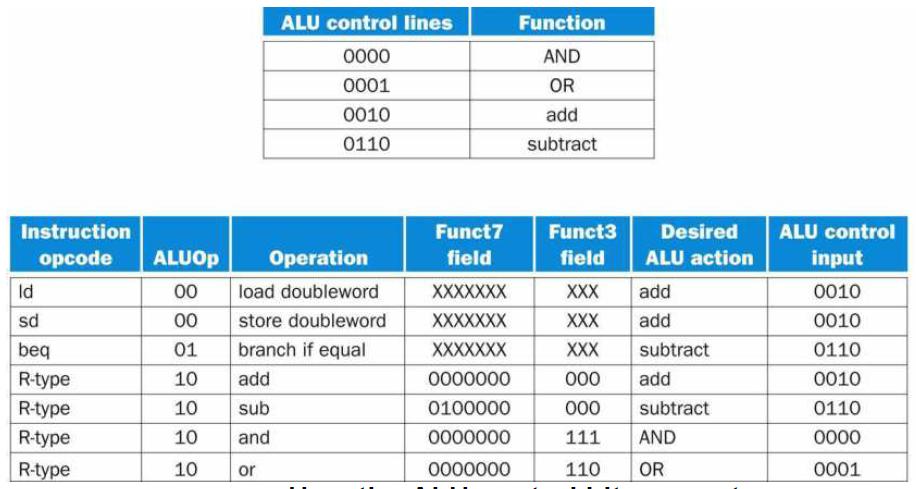

🧠 四、控制信号(关键点🔥)

ALU 并不知道要做什么

👉 是 Control Unit 告诉它

例如:

| 指令 | ALU 控制 |

|---|---|

| ADD | ADD |

| SUB | SUB |

| AND | AND |

| OR | OR |

👉 所以:

ALU = 执行者

Control Unit = 指挥者

💻 五、完整 Verilog 实现(最小 RV32I ALU)

下面是一个可直接使用的 ALU 模块👇

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 |

module alu ( input [31:0] a, // operand A input [31:0] b, // operand B input [3:0] alu_op, // control signal output reg [31:0] result, output zero // zero flag (for branch) ); // ALU operation encoding localparam ADD = 4'b0000; localparam SUB = 4'b0001; localparam AND_ = 4'b0010; localparam OR_ = 4'b0011; localparam XOR_ = 4'b0100; localparam SLT = 4'b0101; localparam SLL = 4'b0110; localparam SRL = 4'b0111; always @(*) begin case (alu_op) ADD: result = a + b; SUB: result = a - b; AND_: result = a & b; OR_: result = a | b; XOR_: result = a ^ b; SLT: result = ($signed(a) < $signed(b)) ? 1 : 0; SLL: result = a << b[4:0]; SRL: result = a >> b[4:0]; default: result = 32'b0; endcase end assign zero = (result == 32'b0); endmodule |

🔥 六、关键设计点(必须理解)

1️⃣ 组合逻辑

|

1 2 |

always @(*) |

👉 没有时钟

👉 输入变化 → 输出立即变化

2️⃣ zero 信号(分支用)

|

1 2 |

assign zero = (result == 0); |

👉 用于:

|

1 2 |

BEQ x1, x2, label |

3️⃣ 位移操作

|

1 2 |

b[4:0] |

👉 RV32I 只使用低5位作为 shift amount

🚨 七、常见错误

❌ 忘记 signed 比较

👉 SLT 必须用 $signed

❌ shift 用错位宽

👉 会导致错误结果

❌ 控制信号不统一

👉 ALU 和 Control Unit 对不上

⚡ 八、从“代码”到“电路”

你写的 Verilog:

|

1 2 |

result = a + b; |

在 FPGA 里变成:

👉 加法器电路

👉 门级逻辑

👉 关键认知:

你不是在写程序

你在定义电路行为

🚀 九、下一步

接下来你将进入最核心部分:

👉 《Datapath 是什么?一张图看懂 CPU》

你将:

📌 总结

👉 一句话:

ALU 不是“计算工具”,它是“计算本身”

除教程外,本网站大部分文章来自互联网,如果有内容冒犯到你,请联系我们删除!