下面是你 RV32I 系列第4篇(核心工程篇),可以直接发布到 2743.com👇

🚀 从 Datapath 到 CPU:实现一个最小 RV32I

你已经知道了:

- Register File

- ALU

- Datapath

现在,真正的关键来了:

👉 把它们连起来,做一个能运行的 CPU

🧠 一、目标是什么?

我们要做的不是“完整 CPU”

👉 而是一个:

最小可运行 RV32I CPU

🎯 支持指令(够用即可)

|

1 2 3 4 5 6 |

ADD ADDI LW SW BEQ |

👉 只要这几个,就可以跑程序

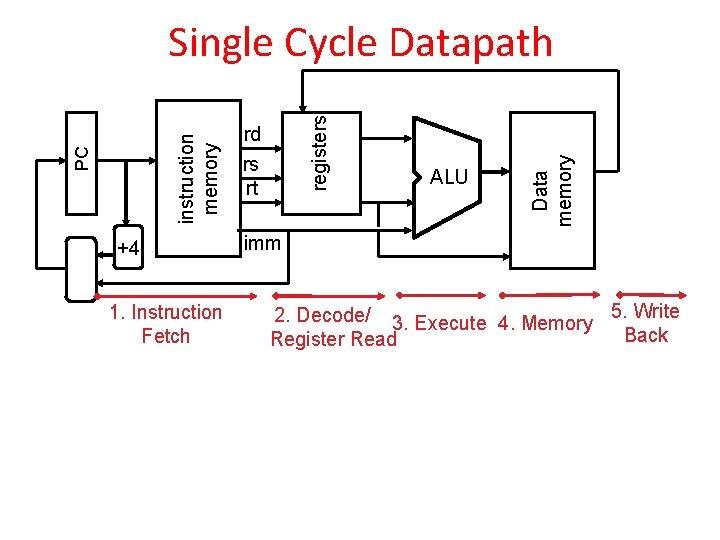

🏗️ 二、整体结构(核心)

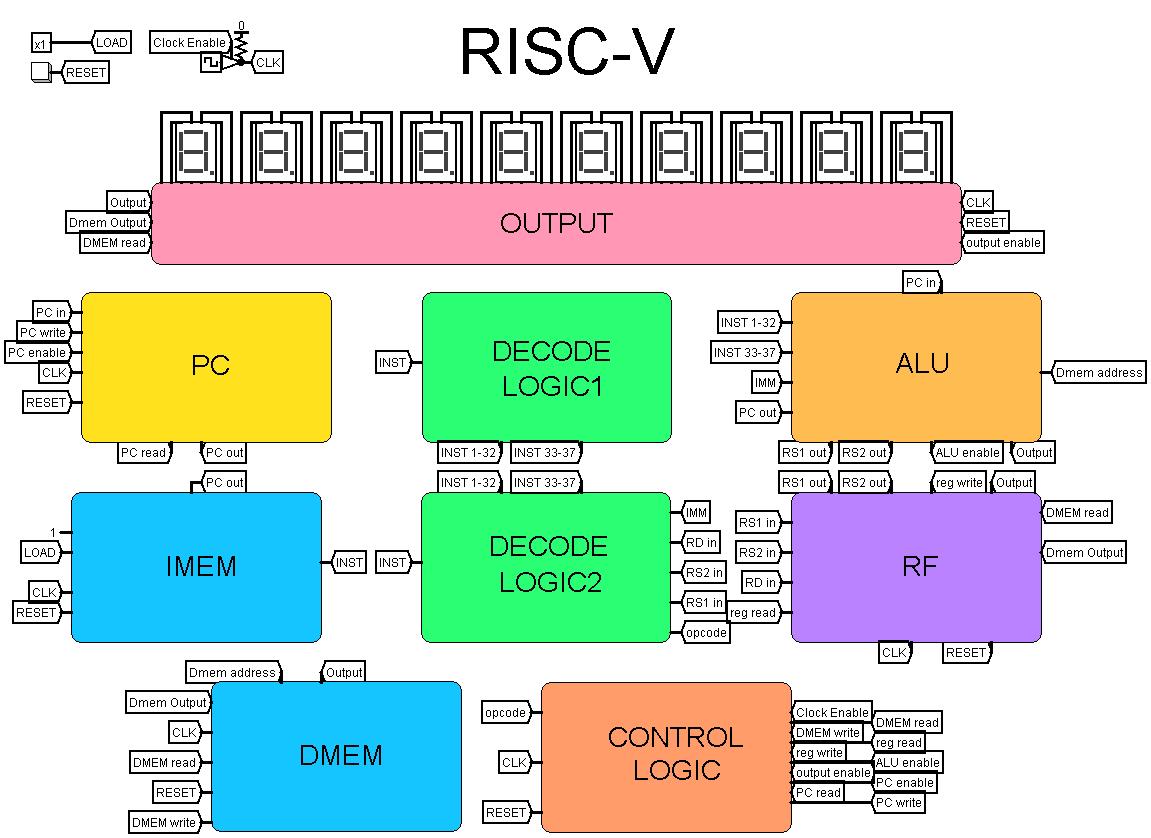

👉 一个最小 CPU 包含:

👉 关键不是模块

👉 是:

|

1 2 |

它们如何连接 |

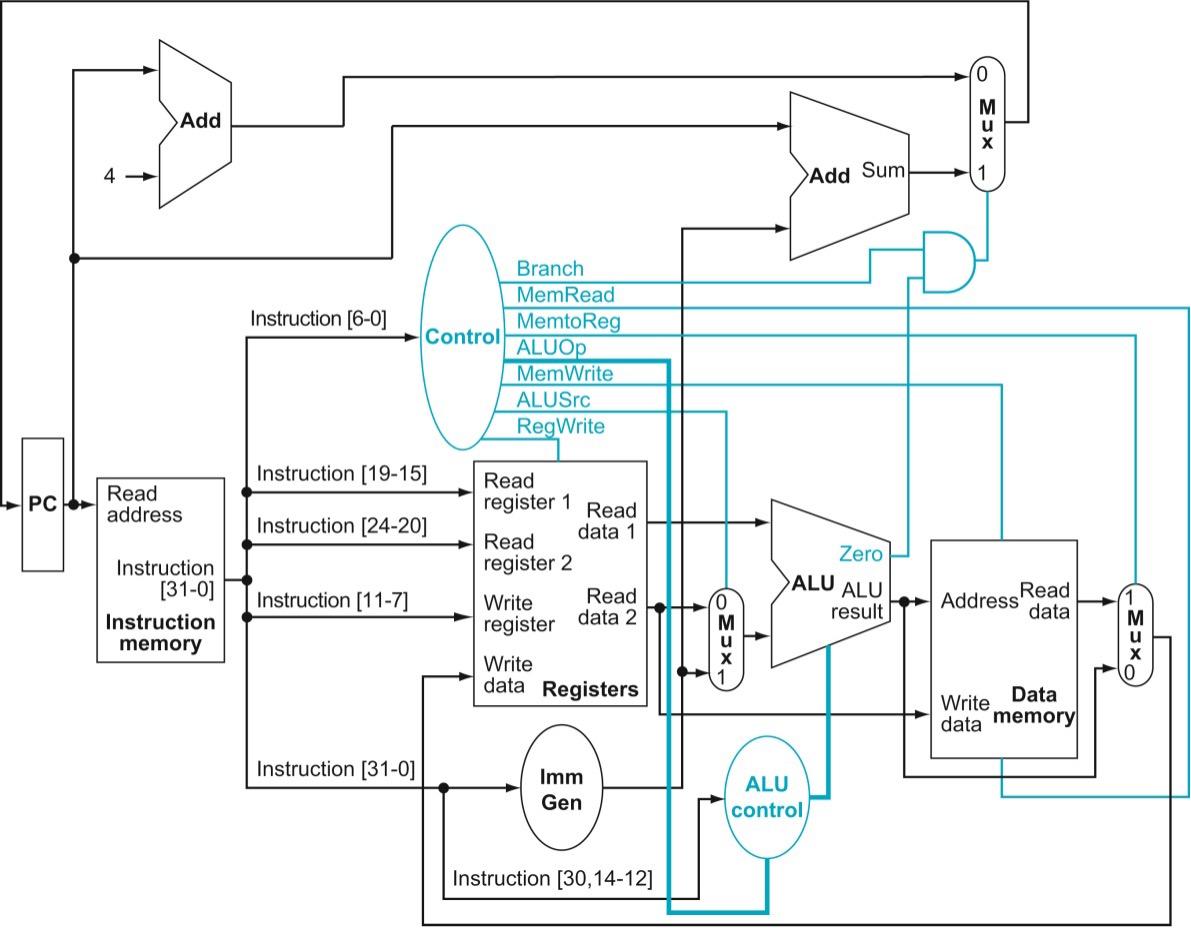

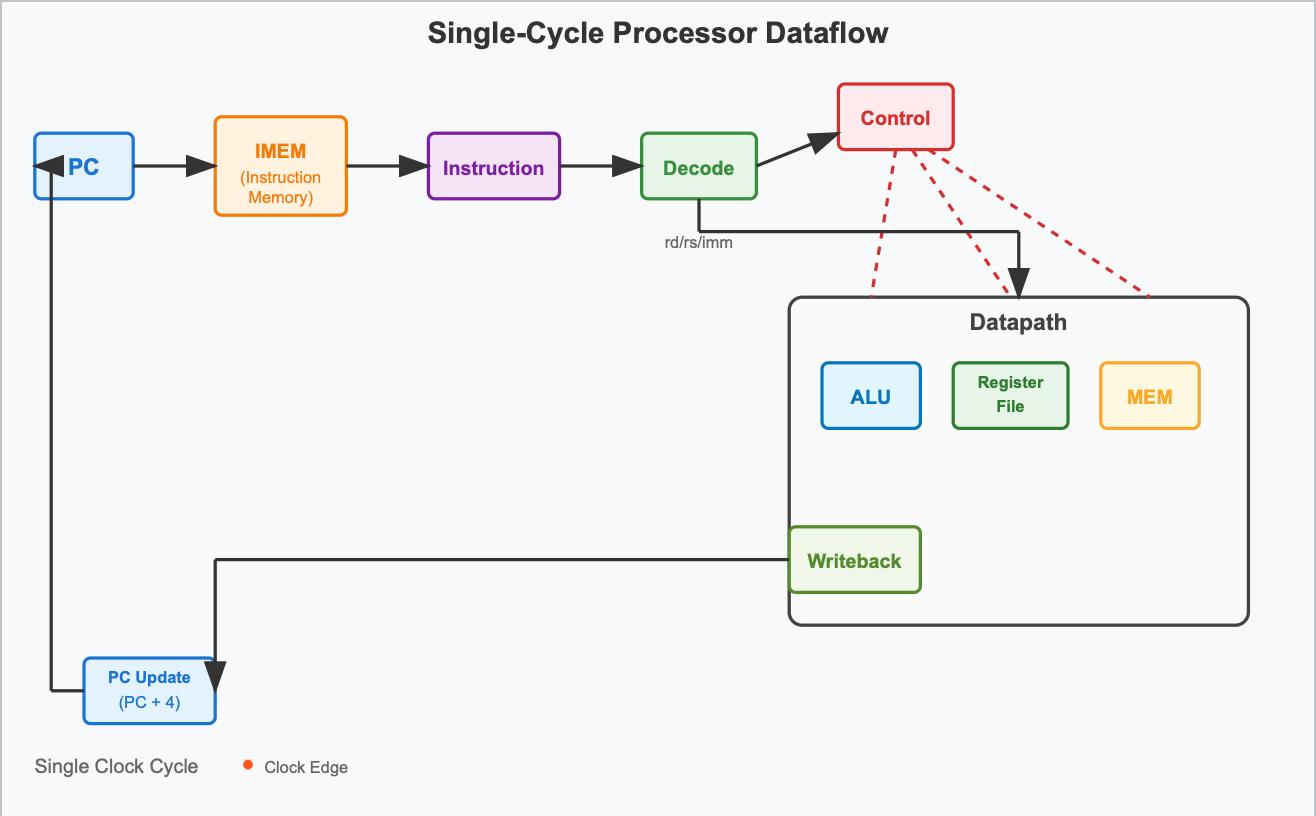

🔄 三、数据流(真正的CPU)

以这条指令为例:

|

1 2 |

ADD x3, x1, x2 |

👉 CPU内部发生:

1️⃣ PC → 取指令

2️⃣ 解码(知道是ADD)

3️⃣ 读取寄存器(x1, x2)

4️⃣ ALU计算

5️⃣ 写回寄存器

👉 这就是完整执行过程

⚙️ 四、模块连接(关键逻辑)

1️⃣ PC

|

1 2 3 4 5 6 |

reg [31:0] pc; always @(posedge clk) begin pc <= pc + 4; end |

2️⃣ 指令获取

|

1 2 3 4 |

wire [31:0] instr; assign instr = instr_mem[pc[9:2]]; |

3️⃣ 解码

|

1 2 3 4 |

wire [4:0] rs1 = instr[19:15]; wire [4:0] rs2 = instr[24:20]; wire [4:0] rd = instr[11:7]; |

4️⃣ Register File

👉 从之前模块复用

5️⃣ ALU连接

|

1 2 3 4 5 6 7 8 9 |

wire [31:0] alu_result; alu u_alu ( .a(reg1), .b(reg2), .alu_op(alu_ctrl), .result(alu_result) ); |

6️⃣ 写回

|

1 2 3 4 5 |

always @(posedge clk) begin if (reg_write) regs[rd] <= alu_result; end |

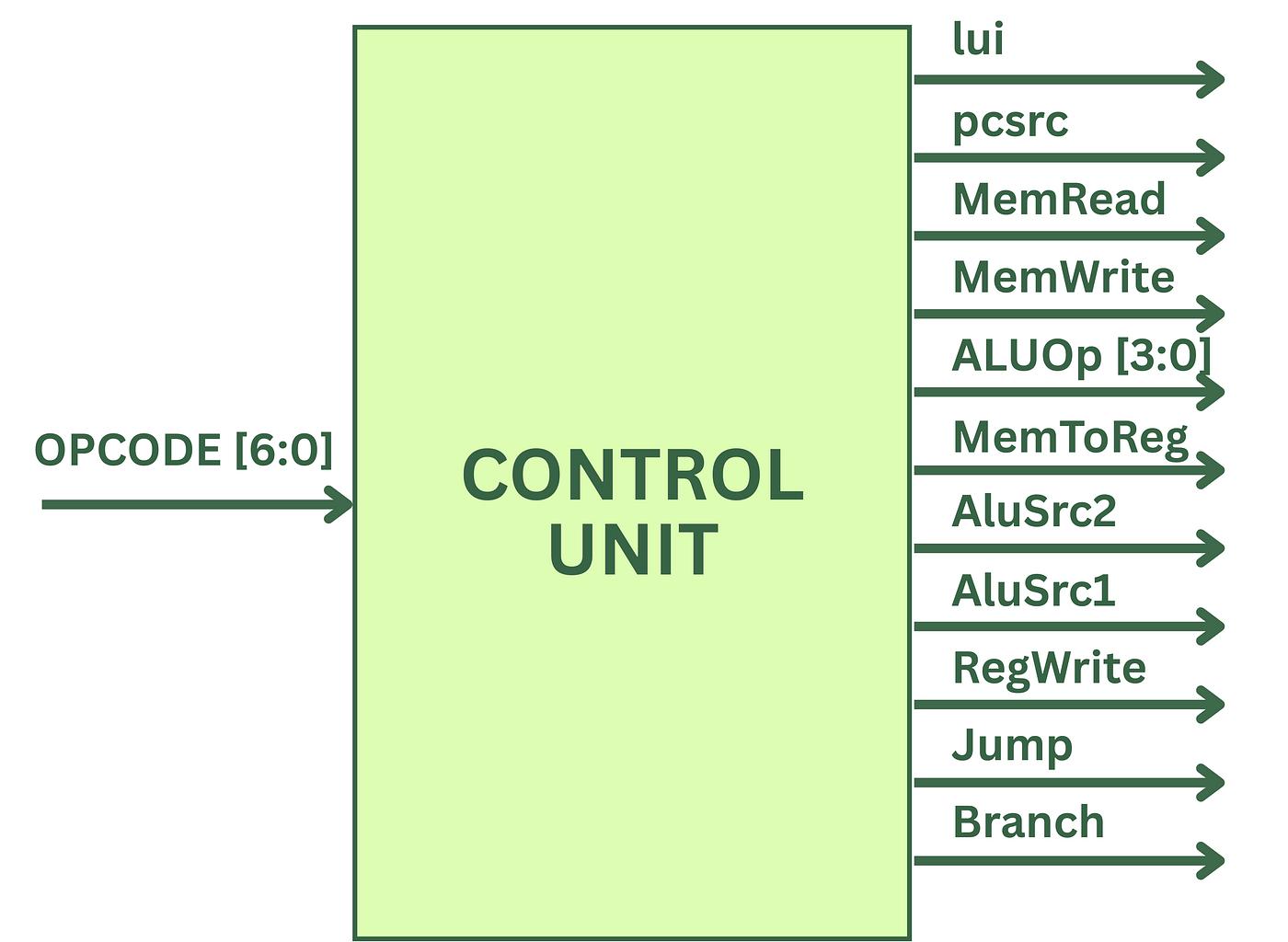

🧠 五、Control Unit(简化版)

👉 最小实现:

|

1 2 3 4 5 6 7 8 9 |

always @(*) begin case (opcode) 7'b0110011: alu_ctrl = ADD; // R-type 7'b0000011: alu_ctrl = ADD; // LW 7'b0100011: alu_ctrl = ADD; // SW default: alu_ctrl = ADD; endcase end |

👉 这里可以非常简单

👉 因为我们只支持少量指令

🔥 六、最小CPU组合(关键认知)

👉 你现在做的不是:

❌ 写程序

👉 而是:

|

1 2 |

搭一个数据流系统 |

👉 所有模块:

- Register → 提供数据

- ALU → 计算

- Memory → 存储

- Control → 控制路径

👉 合在一起:

👉 就是 CPU

⚡ 七、测试(必须做)

写一个最简单程序:

|

1 2 |

int a = 1 + 2; |

👉 编译 → hex → 加载到 instruction memory

👉 如果寄存器得到 3:

🎉 你成功了

🚨 八、常见问题

❌ PC 没更新

👉 程序卡住

❌ decode 错误

👉 指令乱执行

❌ 写回失败

👉 结果不对

🚀 九、你刚刚做了什么?

👉 很多人没意识到:

你刚刚:

做了一个CPU

👉 虽然很简单

👉 但本质已经完整

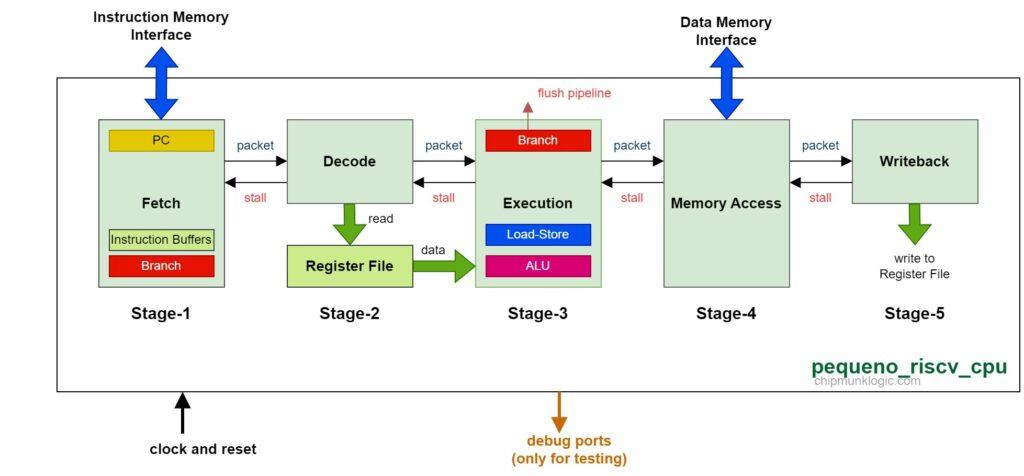

🔥 十、下一步(关键进阶)

现在你有:

👉 单周期 CPU

👉 下一步:

👉 《Pipeline:让 CPU 快10倍的关键》

📌 总结

- CPU = 模块 + Datapath + Control

- RV32I 最小实现是可行的

- 只需少量指令即可运行程序

👉 一句话:

CPU不是“复杂的机器”,而是“简单模块的组合”

除教程外,本网站大部分文章来自互联网,如果有内容冒犯到你,请联系我们删除!