5nm才刚尝上鲜,台积电的3nm厂房也已竣工,甚至传出2nm工艺取得突破的消息。

眼看着摩尔定律极限将至,下一步突破,恐怕就要看碳纳米管的了。

毕竟,芯片制造工艺达到5nm,就意味着单个晶体管栅极的长度仅为10个原子大小。而碳纳米晶体管的直径仅为1nm。碳基芯片是指以碳材料(主要是碳纳米管和石墨烯)作为核心材料制成的新型芯片。它不同于传统以硅为基础的芯片,是一种面向未来的信息处理器件,被认为是“后摩尔时代”的关键技术之一。

碳材料中,碳纳米管是由碳原子组成的中空管状结构,具有极高的电子迁移率,理论上可以让电子以非常快的速度移动,远高于硅材料。而石墨烯是由碳原子构成的单层二维材料,不仅导电性能优秀,强度也很高,并且非常柔韧,适合用于柔性电子设备。研发碳基芯片的主要原因,是因为目前的硅基芯片正在逐步接近其物理极限。随着晶体管不断微缩,芯片面临一系列问题,比如量子效应导致的不稳定性、电流泄漏、发热严重、能耗高等。摩尔定律的持续推进越来越困难,这迫使人们寻找新的材料来突破技术瓶颈。

并且,导电更快、效率更高。与传统硅基芯片相比,碳基芯片具有良好的导热性能,并且相同的面积算力更是达到了惊人的10倍以上。考虑到碳基芯片,具有3D叠加性质,未来出现超过硅基芯片100倍性能的手机处理器也不足为奇。碳材料恰好具有一系列优异性能:它们能实现更快的运算速度、更低的能耗、更高的散热效率,而且可以做成柔性芯片,应用于可穿戴设备、智能织物等新型产品中。此外,碳基芯片有可能成为新计算架构的核心,比如类脑计算或量子计算,因此它不仅仅是硅芯片的延续,更有可能开辟一条全新的技术路径。

但从1998被提出至今,碳纳米管芯片仍存在一系列设计、制造和功能上的问题,比如其在逻辑电路中充当开关时的控制问题。

现在,由台积电首席科学家黄汉森领导,来自台积电、斯坦福大学和加州大学圣地亚哥分校的研究人员,提出了一种新的制造工艺,能更好地控制碳纳米管晶体管。

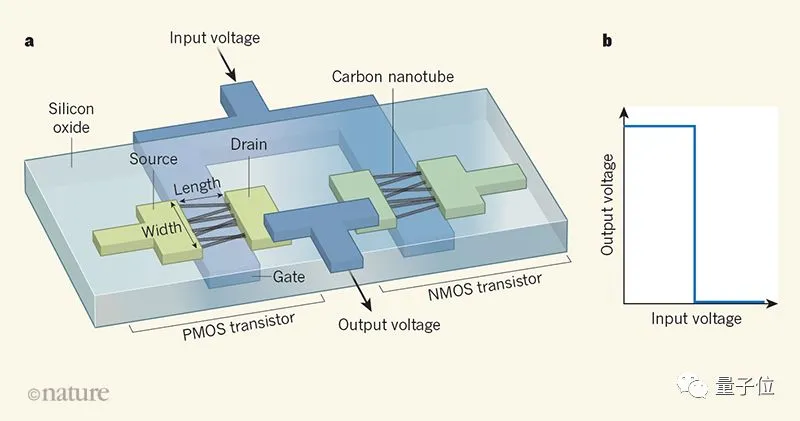

并且,仿真实验的结果表明,用这一方法制造出的碳纳米管元件,与基于CMOS(互补式金属氧化物半导体)的硅元件性能更为接近。

新的栅极电介质工艺

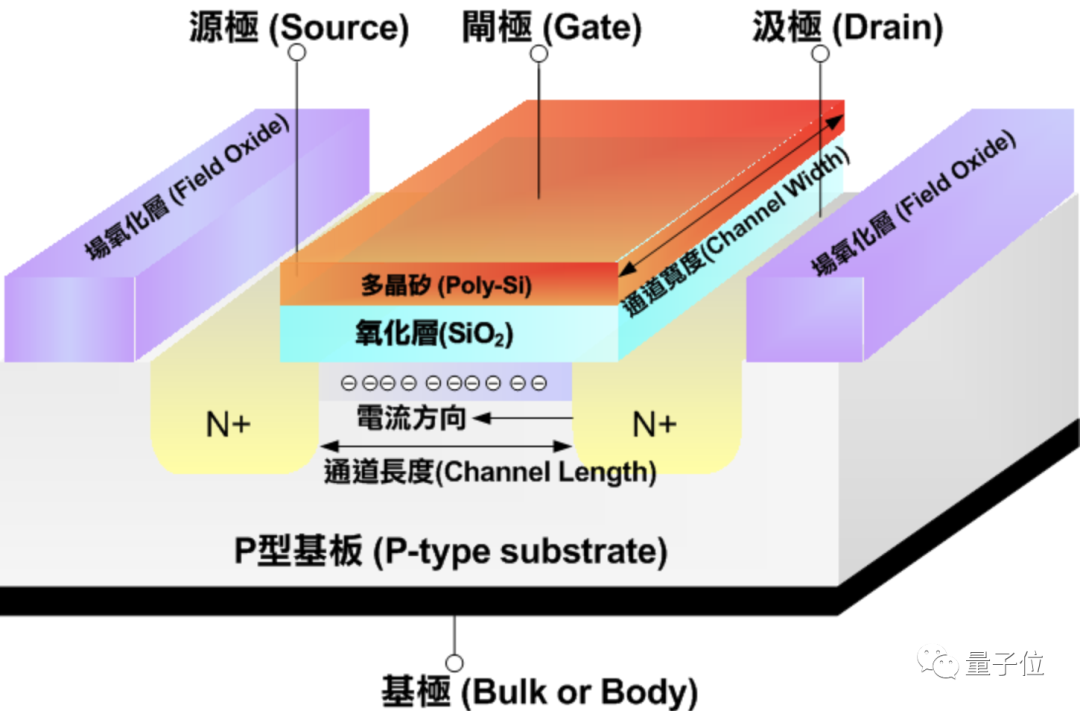

在进入正题之前,不妨先来了解一下栅极电介质。

这是位于栅极(gate)和晶体管沟道区域之间的一层绝缘层。

当晶体管在逻辑电路中充当开关时,栅极上的电压会在沟道区域产生电场,从而切断电流的流动,控制下方沟道的导通和关断。

△CMOS截面图,图源:维基百科

最早,这一绝缘层由二氧化硅构成。但随着硅晶体管尺寸的不断缩小,绝缘层也不得不变得越来越薄,以便用更少的电压来控制电流,降低能耗。

这时候,二氧化硅就不再适用了:绝缘层太薄,那么由于量子力学的隧穿效应,实际上任何电荷都能穿透它,造成能量浪费。

于是,半导体领域的研究人员搬出了一种具有较高介电常数(即高k)的介质材料——二氧化铪。介电常数高,也就意味着更厚的二氧化铪层,就能实现更薄的二氧化硅层的性能。

碳纳米管晶体管上同样采用了二氧化铪栅极电介质。但新的问题出现了:

沉积高k电介质的方法是原子层沉积。这一方法需要一个“起始点”,在硅中,就是表面自然形成的薄薄氧化层。

但碳纳米管不会自然形成氧化层啊,这就导致它并不能为沉积提供“起始点”。

纳米管的瑕疵倒是可以形成沉积点,但这又会限制其导电能力。

那么,怎么才能在不影响其性能的情况下,解决这个棘手的问题呢?

这时候,我们书归正传,来看看这项新研究提出的解决方案:

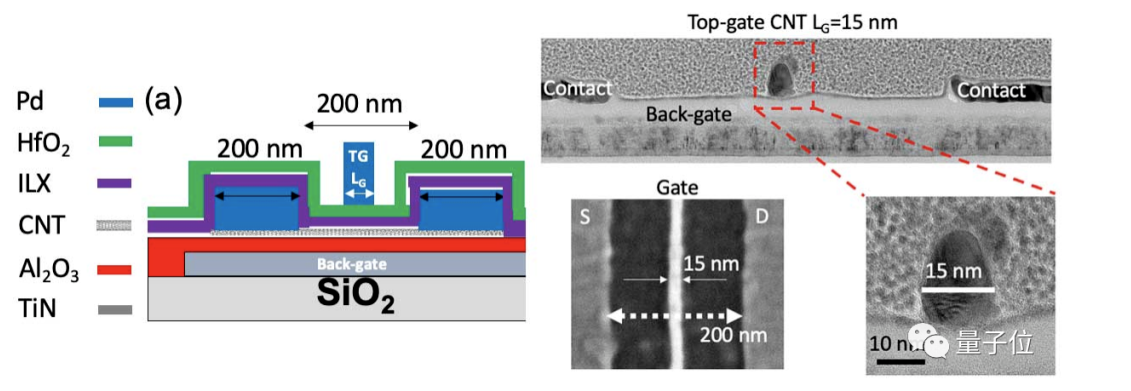

在碳纳米管和二氧化铪之间加入一个中间k介质。

△中间圆形为纳米管,上部黑色为栅极

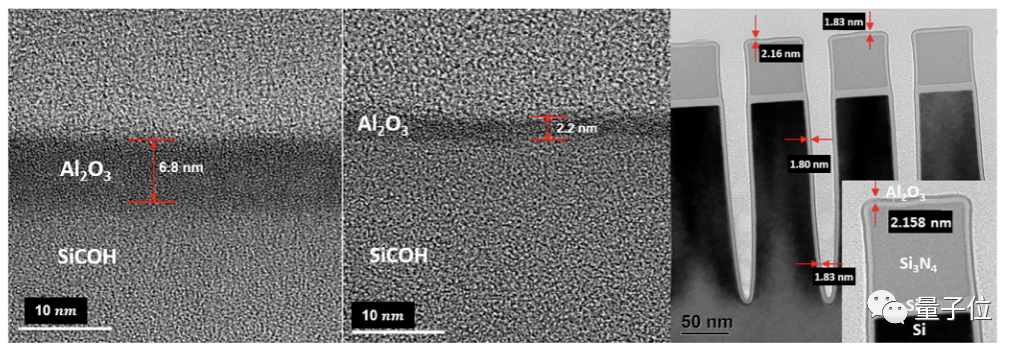

具体而言,根据台积电Matthias Passtlack和加州大学圣地亚哥分校Andrew Kummel教授的研究,是将二氧化铪和氧化铝相结合。

其中,氧化铝采用加州大学圣地亚哥分校发明的纳米雾(nanofog)技术制备。氧化铝会像水蒸气凝结成雾一样,凝结成簇,覆盖在纳米管表面。

以氧化铝界面为基础,二氧化铪原子层沉积的过程就能展开了。

实验结果

两种电介质的综合电特性,使得研究人员能够在一个直径只有15nm的栅极下,构造一个厚度小于4nm的栅极电介质装置。

并且,根据这一方法制备的碳纳米管元件,具备与基于CMOS的硅元件形似的开/关电流比特性。

仿真实验的结果还表明,即使是栅极电介质更薄、尺寸更小的元件,也同样work。

碳纳米管取代硅,还有多远?

当然,控制问题仅仅只是一方面。

想要让碳纳米管芯片真正具备与硅基芯片一战的实力,还有许多亟待解决的挑战。

比如如何制备超高半导体纯度、顺排、高密度、大面积均匀的碳纳米管阵列。比如如何对碳纳米管进行掺杂以增加栅极两侧的载流子数量……

不过近年以来,也不断有好消息传出。

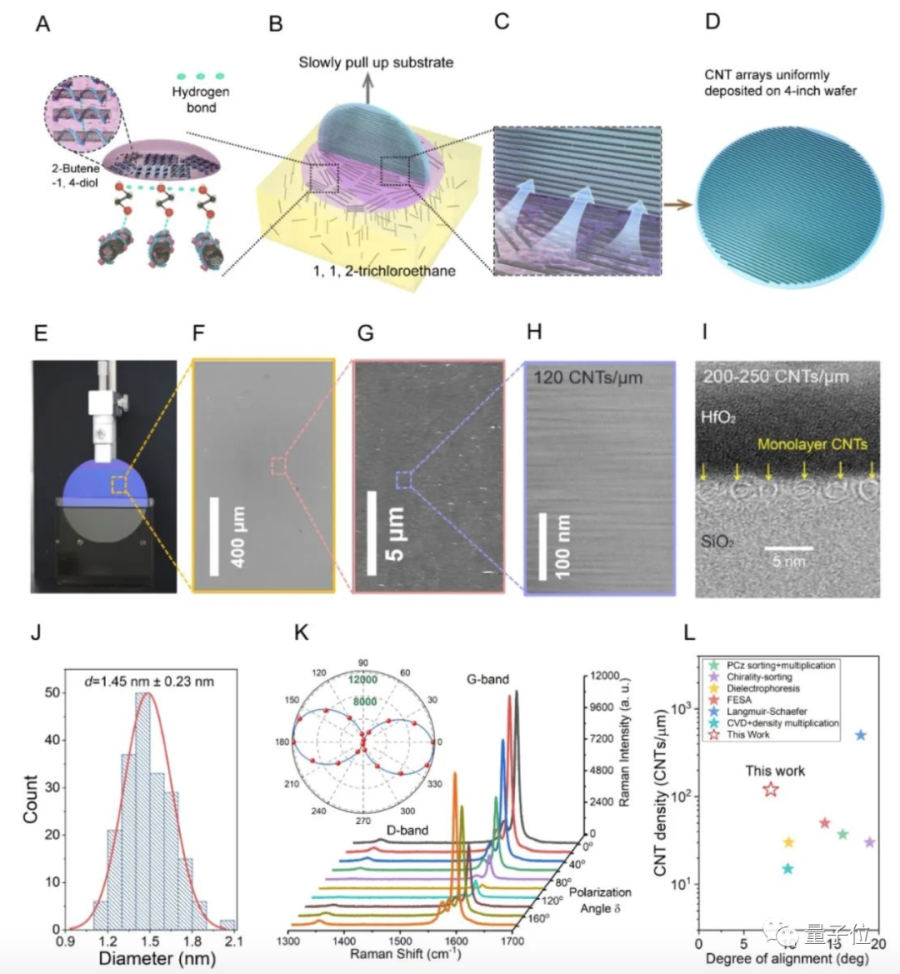

北京大学彭练矛院士团队,今年5月份就在Science上发文,发展了一套可以制备排列碳纳米管的技术,排列密度达到每微米200-250根。

去年,MIT研究团队发布全球首款碳纳米管通用计算芯片,使用超过14000个晶体管,并且碳纳米管产率为100%。也就是说,14000个晶体管每个都有效,没有一个报废。

黄汉森就表示:

我们正在一件一件地搬除障碍。

如果我们能把所有解决方案组合在一起,我们就能击败硅。

一、什么是碳基芯片?

碳基芯片并不是一个具体的单一器件,而是指采用碳材料来替代传统硅材料所构建的各类微电子元件和电路。常见的两类碳材料:

1. 碳纳米管(Carbon Nanotube, CNT)

2. 石墨烯(Graphene)

-

是一种二维单原子层碳材料,具有超高的导电率和热导率,且强度极高。

-

可用于高速开关器件、柔性电子、传感器等。

二、为什么要研发碳基芯片?

1. 硅基芯片接近物理极限

-

随着摩尔定律逼近极限,硅晶体管尺寸已缩小到几纳米,继续缩小将面临量子隧穿效应、发热严重、能耗高等问题。

-

硅材料本身的电子迁移率和物理性能也接近瓶颈,进一步提升性能变得困难。

2. 碳材料性能优异

-

电子迁移率高:比硅高数十倍,理论上可以实现更高的运算速度。

-

能耗低:开关速度快但能耗更低,有助于打造低功耗芯片。

-

散热能力强:热导率极高,有助于解决高性能芯片的散热难题。

-

柔性可弯曲:尤其石墨烯,适合柔性电子产品(如可穿戴设备、柔性屏幕)。

3. 推动下一代计算架构

三、现实挑战

虽然碳基芯片具有巨大潜力,但目前仍面临诸多技术瓶颈:

-

大规模制备困难:如碳纳米管的一致性、排列、纯度控制问题仍未完全解决。

-

集成工艺尚不成熟:与现有 CMOS 工艺的融合还需深入研究。

-

成本高、稳定性差:与成熟的硅工艺相比,碳材料的可控性和可靠性仍需改进。

四、总结

研发碳基芯片的主要原因,是因为目前的硅基芯片正在逐步接近其物理极限。随着晶体管不断微缩,芯片面临一系列问题,比如量子效应导致的不稳定性、电流泄漏、发热严重、能耗高等。摩尔定律的持续推进越来越困难,这迫使人们寻找新的材料来突破技术瓶颈。

碳材料恰好具有一系列优异性能:它们能实现更快的运算速度、更低的能耗、更高的散热效率,而且可以做成柔性芯片,应用于可穿戴设备、智能织物等新型产品中。此外,碳基芯片有可能成为新计算架构的核心,比如类脑计算或量子计算,因此它不仅仅是硅芯片的延续,更有可能开辟一条全新的技术路径。

碳基芯片的研究还处于早期阶段,面临很多挑战,比如碳纳米管在制造过程中难以排列整齐、石墨烯大规模制备技术尚不成熟、工艺难度高、成本较贵等等。这些问题限制了它的商用化和量产。

碳基芯片的研发是应对硅基技术瓶颈、推动信息技术革新的关键一步。虽然仍处于研发和实验阶段,但一旦实现突破,可能会彻底改变未来的计算格局与电子产品形态。

碳基芯片为什么不能大规模生产?

1. 材料一致性和纯度难以控制

以碳纳米管为例,它有很多种结构(直径、手性不同),但只有其中一部分具有理想的半导体特性。

目前的制备方法难以做到只生成“好用的”碳纳米管,往往混合了金属性和半导体性的纳米管。如果不能分离,器件就会出现短路、无法开关等问题。

石墨烯的问题在于:即使能制备出单层石墨烯,要保证其结构完整、无缺陷、无污染也非常困难,而这对电子性能影响极大。

2. 大规模、可控的排列与连接技术尚不成熟

在芯片制造中,每一个元件的位置必须非常精确(纳米级误差都不允许)。

但碳纳米管很难“按设计”整齐排列,它们容易弯曲、打结、交叉,造成短路或性能不稳定。

即使能控制一个碳纳米管的性能,也很难让成千上万个管子都“井然有序”地布置在芯片上并彼此连接,这直接限制了芯片规模的扩大。

3. 与现有工艺难以兼容

目前主流的芯片生产采用的是成熟的CMOS硅工艺,高度自动化,成本低、良品率高。

而碳材料的制备、转移、刻蚀、封装等流程,和传统工艺有较大差异。

要么要重新建立生产线,成本极高;要么要让碳材料“适配”硅工艺,这又对材料本身提出了极高要求。

4. 良品率低、稳定性差

即使成功做出一些碳基芯片,其性能一致性、长期稳定性也很难保证。实验中常常出现一部分器件性能很好,另一部分完全无法使用,这使得量产极不经济。

而商用芯片对可靠性和批量生产能力要求极高,这也是碳基芯片尚未进入市场的原因之一。

5. 测试与标准体系缺失

碳基芯片还缺乏一个完善的测试、评价标准体系。不像硅芯片那样有成熟的产业链和质量检测体系,碳芯片的性能评估、寿命预测等环节尚不统一,这也阻碍了它从实验室走向市场。

碳基芯片的材料太“优秀”,但太难“驯服”。从制备到控制,从排列到集成,从性能到成本,目前都不具备成熟、稳定、大批量工业化的条件。

参考链接:

https://spectrum.ieee.org/nanoclast/semiconductors/devices/scaleddown-carbon-nanotube-transistors-inch-closer-to-silicon-abilities