(一)半导体封测生产流程

晶圆代工厂制造完成的晶圆在出厂前会经过一道电性测试,称为晶圆可接受度测试(Wafer Acceptance Test,WAT),WAT 测试通过的晶圆被送去封测厂。封测厂首先对晶圆进行中测(Chip Probe,CP)。由于工艺原因会引入各种制造缺陷,导致晶圆上的裸 Die 中会有一定量的残次品, CP 测试的目的就是在封装前将这些残次品找出来,缩减后续封测的成本。在完成晶圆制造后, 通过探针与芯片上的焊盘接触,进行芯片功能的测试,同时标记不合格芯片并在切割后进行筛选。 CP 测试完成后进入封装环节,封装工艺流程一般可以分为两个部分,用塑料封装之前的工艺步 骤称为前段操作,在成型之后的工艺步骤称为后段操作。基本工艺流程包括晶圆减薄、晶圆切割、 芯片贴装、固化、芯片互连、注塑成型、去飞边毛刺、上焊锡、切筋成型、打码等。因封装技术 不同,工艺流程会有所差异,且封装过程中也会进行检测。封装完成后的产品还需要进行终测 (Final Test,FT),通过 FT 测试的产品才能对外出货。

(二)半导体封装类型

根据封装材料的不同,半导体封装可分为塑料封装、金属封装、陶瓷封装和玻璃封装。塑料 封装是通过使用特制的模具,在一定的压力和温度条件下,用环氧树脂等模塑料将键合后的半成 品封装保护起来,是目前使用最多的封装形式。金属封装以金属作为集成电路外壳,可在高温、 低温、高湿、强冲击等恶劣环境下使用,较多用于军事和高可靠民用电子领域。陶瓷封装以陶瓷 为外壳,多用于有高可靠性需求和有空封结构要求的产品,如声表面波器件、带空气桥的 GaAs 器件、MEMS 器件等。玻璃封装以玻璃为外壳,广泛用于二极管、存储器、LED、MEMS 传感 器、太阳能电池等产品。其中金属封装、陶瓷封装和玻璃封装属于气密性封装,能够防止水汽和 其他污染物侵入,是高可靠性封装;塑料封装是非气密性封装。

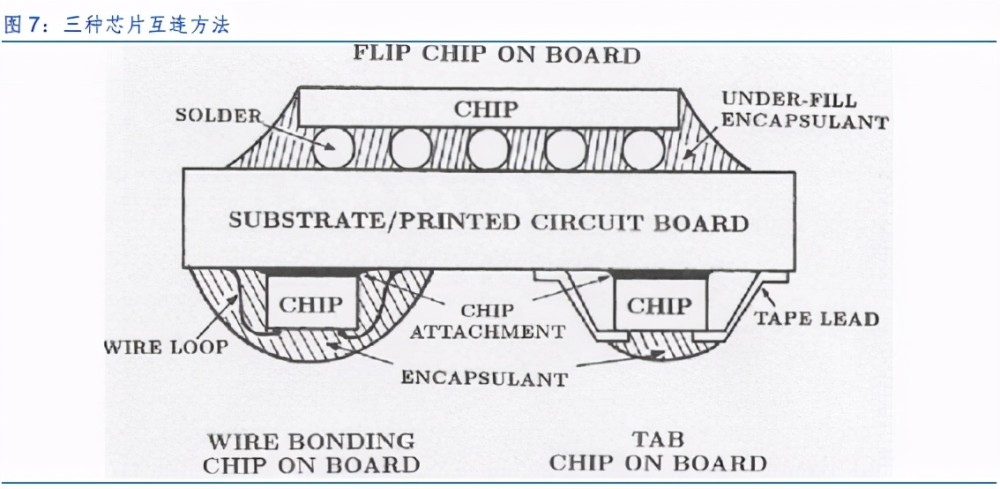

根据封装互连的不同,半导体封装可分为引线键合(适用于引脚数 3-257)、载带自动焊(适 用于引脚数 12-600)、倒装焊(适用于引脚数 6-16000)和埋入式。引线键合是用金属焊线连接 芯片电极和基板或引线框架等。载带自动焊是将芯片上的凸点与载带上的焊点焊接在一起,再对 焊接后的芯片进行密封保护的一种封装技术。倒装焊是在芯片的电极上预制凸点,再将凸点与基 板或引线框架对应的电极区相连。埋入式是将芯片嵌入基板内层中。

根据与 PCB 连接方式的不同,半导体封装可分为通孔插装类封装和表面贴装封装。通孔插 装器件是 1958 年集成电路发明时最早的封装外形,其外形特点是具有直插式引脚,引脚插入PCB 上的通孔后,使用波峰焊进行焊接,器件和焊接点分别位于 PCB 的两面。表面贴装器件是 在通孔插装封装的基础上,随着集成电路高密度、小型化及薄型化的发展需要而发明出来的,一 般具有“L”形引脚、“J”形引脚、焊球或焊盘(凸块),器件贴装在 PCB 表面的焊盘上,再使 用回流焊进行高温焊接,器件与焊接点位于 PCB 的同一面上。

目前,引线键合技术因成本相对低廉,仍是主流的封装互联技术,但它不适合对高密度、高 频有要求的产品。倒装焊接技术适合对高密度、高频及大电流有要求的产品,如电源管理、智能 终端的处理器等。TAB 封装技术主要应用于大规模、多引线的集成电路的封装。

(三)先进封装是后摩尔时代的必然选择

1、封装技术发展史

封装技术的发展需要满足电子产品小型化、轻量化、高性能等需求,因此,封装技术过去和 未来的发展趋势均是高密度、高脚位、薄型化、小型化。 根据《中国半导体封装业的发展》,半导体封装技术的发展历史可大致分为以下五个阶段:

第一阶段:20 世纪 70 年代以前(通孔插装时代),封装技术是以 DIP 为代表的针脚插装, 特点是插孔安装到 PCB 板上。这种技术密度、频率难以提高,无法满足高效自动化生产的要求。

第二阶段:20 世纪 80 年代以后(表面贴装时代),用引线替代第一阶段的针脚,并贴装到 PCB 板上,以 SOP 和 QFP 为代表。这种技术封装密度有所提高,体积有所减少。 第三阶段:20 世纪 90 年代以后(面积阵列封装时代),该阶段出现了 BGA、CSP、WLP 为代表的先进封装技术,第二阶段的引线被取消。这种技术在缩减体积的同时提高了系统性能。

第四阶段:20 世纪末以后,多芯片组件、三维封装、系统级封装开始出现。

第五阶段:21 世纪以来,主要是系统级单芯片封装(SoC)、微机电机械系统封装(MEMS)。 目前全球半导体封装的主流正处在第三阶段的成熟期和快速发展期,以 CSP、BGA、WLP 等主要封装形式进入大规模生产时期,同时向第四、第五阶段发展。从发展历史可以看出,半导 体封装技术的发展趋势可归纳为有线连接到无线连接,芯片级封装到晶圆级封装,二维封装到三 维封装。

2、封装技术

根据技术先进性,封装技术可分为传统封装技术和先进封装技术两大类。传统封装技术包括 DIP、SOP、QFP、WB BGA 等,先进封装技术包括 FC、WLP、FO、3D 封装、系统级封装等。 随着晶圆代工制程不断缩小,摩尔定律逼近极限,先进封装是后摩尔时代的必然选择。

(1)SIP/DIP

单列直插封装(Single Inline Package,SIP)的引脚从封装体的一个侧面引出,排列成一 条直线,SIP 的引脚数量一般为 2-23 个。

双列直插封装(Dual Inline Package,DIP)的外形为长方形,在两侧有两排平行的金属引 脚,称为排针。DIP 封装的产品需要插入到具有 DIP 结构的芯片插座上,或者直接插在有相同焊 孔数和几何排列的电路板上再进行焊接。引脚数一般不超过 100,适合中小规模集成电路封装。

(2)SOP/QFP

小外形封装(Small Out-Line Package,SOP)的引脚从封装两侧引出,呈海鸥翼状(L 字 形)。

方型扁平式封装(Quad Flat Package,QFP)的管脚很细,引脚之间距离很小,可实现更 多的 I/O 数,但仍受限于 0.3mm 的引脚间距极限。

(3)BGA

球栅阵列封装(Ball Grid Array Package,BGA)用焊球代替周边引线,成阵列分布于封装 基板的底部平面上,是在生产具有数百根引脚的集成电路时,针对封装必须缩小的难题所衍生出 的解决方案。

与上一代的 QFP 相比,BGA 在减小体积和重量的情况下增加了 I/O 数量,但引脚的间距可 以做得更大,成品率反而提高了;由于焊球间距明显短于引线,BGA 电性能更好;焊球的共面 性也改善了散热性。

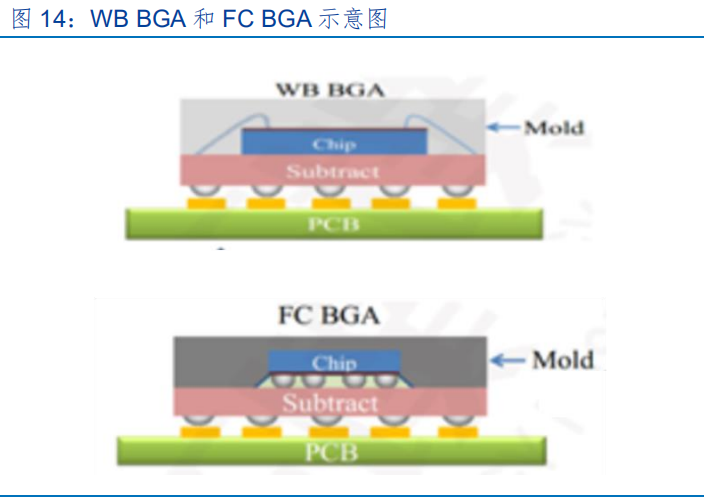

根据芯片的位置不同可分为芯片表面向上和向下两种;按焊球排列方式可为球栅阵列均匀分 布、球栅阵列交错分布、球栅阵列周边分布等;按密封方式可分为模制密封和浇注密封等;按基 板材料可分为塑料球栅阵列 PBGA( Plastic Ball Grid Array)、陶瓷球栅阵列 CBGA(Ceramic Ball Grid Array)、载带球阵列 TBGA(Tape Ball Grid Array)等。

(4)FC

倒装(Flip Chip,FC)技术由 IBM 在 20 世纪 60 年代研发出来,20 世纪 90 年代后期形成 规模化量产,主要应用于高端领域产品。随着铜柱凸块技术的出现,结合消费电子产品的快速发 展和产品性能的需求,越来越多的产品转向倒装芯片封装。

所谓“倒装”是相对于传统的金属线键合连接方式(Wire Bonding,WB)而言的。传统 WB 工艺,芯片通过金属线键合与基板连接,电气面朝上;倒装芯片工艺是指在芯片的 I/O 焊盘 上直接沉积,或通过 RDL 布线后沉积凸块(Bump),然后将芯片翻转,进行加热,使熔融的焊 料与基板或框架相结合,芯片电气面朝下。与 WB 相比,FC 封装技术的 I/O 数多;互连长度缩 短,电性能得到改善;散热性好,芯片温度更低;封装尺寸与重量也有所减少。

倒装芯片工艺流程中晶圆减薄、芯片倒装和底部填充是关键工艺。在倒装芯片的工艺中,晶 圆来料上已经完成了凸块的制作,因此晶圆正面并不平整。由于晶圆没有凸块的区域是空心结构, 所以研磨过程中,晶圆会产生振动,容易造成晶圆龟裂甚至破片,尤其是超薄晶圆的研磨,目前 一般采用底部填充工艺技术来解决该问题。在芯片倒装工艺中,需要采用高精度坐标对准技术将 芯片上的凸块焊接在高密度线路基板上,在此过程中,各方应力相互拉扯,基板容易产生翘曲现 象,这会造成焊接出现偏移、冷焊、桥接短路等质量问题。底部填充是在芯片、凸块及基板三种 材料之间填充底部材料,以避免三种材料因膨胀系数不同而产生剪应力破坏,底部填充的关键因 素是黏度、温度、流动长度与时间。

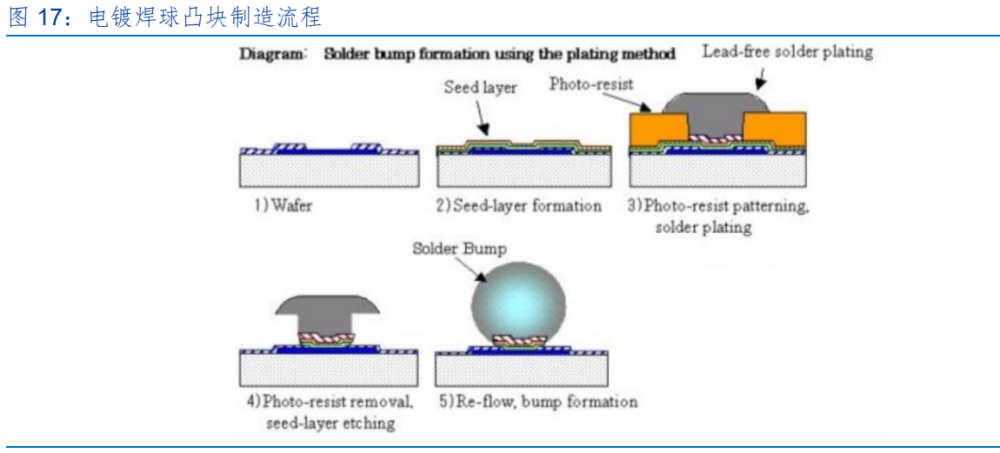

凸块工艺被称为中道工序,是先进封装的核心技术之一,通过高精密曝光、离子处理、电镀 等设备和材料,基于定制的光掩模,在晶圆上实现重布线,允许芯片有更高的端口密度,缩短了 信号传输路径,减少了信号延迟,具备了更优良的热传导性及可靠性。主流的凸块工艺均采用晶 圆级加工,即在整块晶圆表面的所有芯片上加工制作凸块,晶圆级凸块工艺包括蒸发方式、印刷 方式和电镀方式三种,目前业界广泛采用的是印刷方式和电镀方式。晶圆代工厂在凸块工艺方面 具有一定优势。

(5)WLP

晶圆级封装(Wafer Level Packaging,WLP)直接在晶圆上进行大部分或全部的封装测试 程序,之后再进行切割制成单颗芯片。采用这种封装技术,不需要引线框架、基板等介质,芯片 的封装尺寸减小,批量处理也使生产成本大幅下降。

WLP 可分为扇入型晶圆级封装(Fan-In WLP)和扇出型晶圆级封装(Fan-Out WLP)两大 类。扇入型直接在晶圆上进行封装,封装完成后进行切割,布线均在芯片尺寸内完成,封装大小 和芯片尺寸相同;扇出型则基于晶圆重构技术,将切割后的各芯片重新布置到人工载板上,芯片间距离视需求而定,之后再进行晶圆级封装,最后再切割,布线可在芯片内和芯片外,得到的封 装面积一般大于芯片面积,但可提供的 I/O 数量增加。

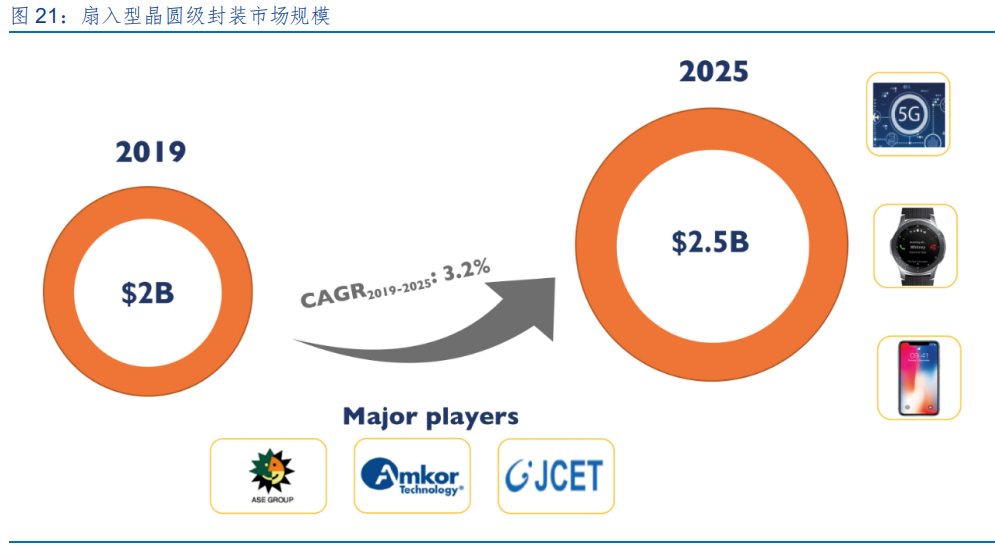

根据 Yole 的数据,全球晶圆级封装 2019 年的市场规模为 33 亿美元,预计 2025 年增加到 55 亿美元,CAGR 为 8.9%。其中扇入型晶圆级封装由 2019 年的 20 亿美元增加到 2025 年的 25 亿美元,CAGR 为 3.2%。2020 年苹果发布的 iPhone12 采用了扇入型晶圆级封装,未来将 会有更多的手机、平板、可穿戴设备采用此封装形式。

(6)FO

扇出(Fan Out,FO)是相对扇入而言,“扇入”只能向内走线,而在扇出型封装中,既可 以向内走线,也可以向外走线,从而可以实现更多的 I/O,以及更薄的封装。目前量产最多的是 晶圆级扇出型产品。 扇出型封装工艺主要分为 Chip first 和 Chip last 两大类,其中 Chip first 又分 Die down 和 Die up 两种。

扇出型封装生产工艺的关键步骤包括芯片放置、包封和布线。芯片放置对速度和精度的要求 很高,放置速度直接决定生产效率,从而影响制造成本;放置精度也是决定后续布线精度的关键 性因素。包封需要对包封材料进行填充和加热,这一过程不仅可能导致已放置好的芯片发生移位, 还有可能因包封材料与芯片的膨胀系数的不同而造成翘曲,这两者都会影响后续的布线环节。布 线成功率是决定最终封装成品率的关键因素,另一方面,布线设备是整个生产设备中最昂贵的, 对制造成本的影响很大。

根据封装芯片数量,扇出型封装分为晶圆级扇出型(Fan-out Wafer Level Packaging, FOWLP)和板级扇出型技术(Fan-out Panel Level Packaging, FOPLP),FOWLP 对单个芯片 进行封装,FOPLP 对多个芯片进行封装。虽然 FOPLP 的增速更快,FOWLP 在未来几年仍占主 导。根据 Yole 的数据,2019-2025 年 FOPLP 的 CAGR 达 57%,FOWLP 的 CAGR 为 14%, 但 FOWLP 在 2025 年的占比仍会在 2/3 以上。eWLB(Embedded Wafer Level Ball Grid Array) 是目前量产规模最大的晶圆级扇出型封装。

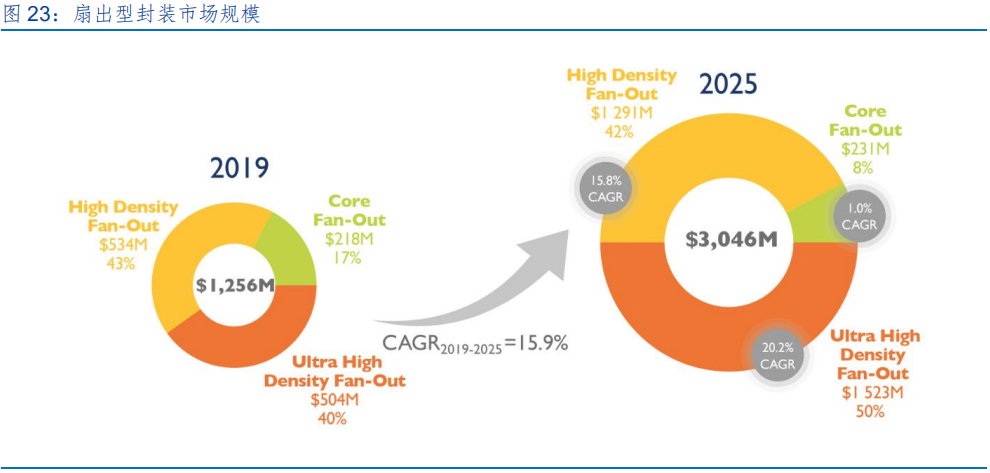

根据密度的高低,Yole 将扇出型封装分为 UHD 扇出(Ultra High Density)、HD 扇出(High Density)和核心扇出三大类。UHD 扇出的需求将随着新的 HPC 产品的出现而增加,预计 2019-2025 年的 CAGR 最高,为 20.2%,到 2025 年市场规模达 15.32 亿美元,占扇出型一半 的市场;HD 扇出的 CAGR 为 15.8%,到 2025 年达 12.91 亿美元;核心扇出增长缓慢,CAGR仅1%。

(7)3D/2.5D 封装

3D 封装又称为叠层芯片封装技术,是指在不改变封装体尺寸的前提下,在同一个封装体内 于垂直方向叠放两个以上芯片的封装技术,它起源于快闪存储器(NOR/NAND)及 SDRAM 的叠层 封装,可以实现不同类型芯片的异质集成,目前在存储芯片上已有较多应用。

3D 封装可采用凸块或硅通孔技术(Through Silicon Via,TSV),TSV 是利用垂直硅通孔完 成芯片间互连的方法,由于连接距离更短、强度更高,能实现更小更薄而性能更好、密度更高、 尺寸和重量明显减小的封装,而且还能用于异种芯片之间的互连。 2.5D 封装是在基板和芯片之间放一个硅中间层,这个中间层通过 TSV 连接上下部分。

(8)SiP

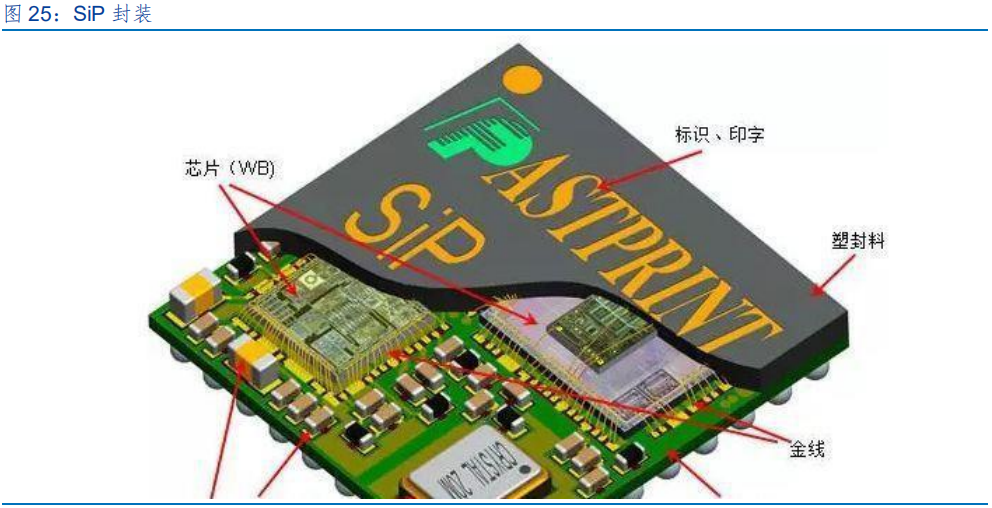

系统级封装(System in Packag,SiP)是将多种功能芯片,包括处理器、存储器、FPGA 等功能芯片集成在一个封装内,从而实现一个基本完整的功能。与系统级芯片(System on Chip,SoC)相对应,不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而 SoC 则是 高度集成的芯片产品。SiP 解决方案需要多种封装技术,如引线键合、倒装芯片、芯片堆叠、晶 圆级封装等,是超越摩尔定律的重要实现路径。

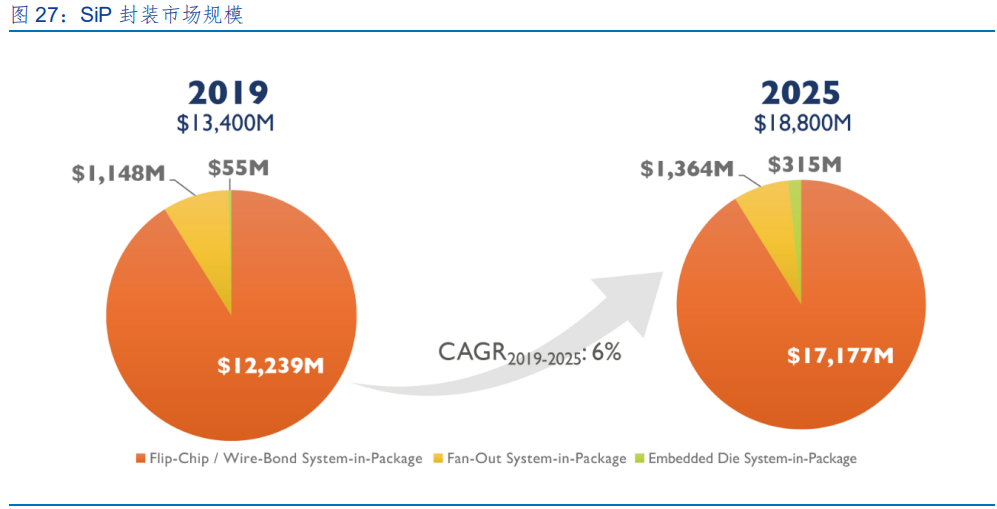

根据 Yole 的数据,2019 年全球 SiP 封装的市场规模为 134 亿美元,预计 2025 年增加到 188 亿美元,CAGR 为 6%。

从应用领域来看,移动设备和消费电子是最大市场,2019-2025 年的 CAGR 为 5%;通讯/ 基础设施和汽车电子紧随其后,两者的 CAGR 均为 11%,高于整体增速。

从使用的封装技术来看,FC/WB SiP 占比超过 90%,2019 年市场规模为 122 亿美元,预计到 2025 年将达到 171 亿美元,2019 年至 2025 年的复合年增长率为 6%。FO SiP 仍受限于成本效益比,参与者需要掌握 FO 技术,所以从 2017 年开始,台积电便是最主要的参与者,2019 年市占率超过 90%。

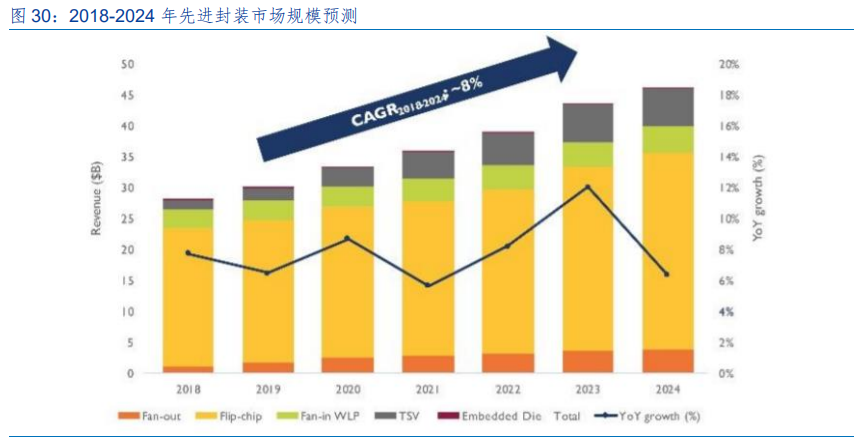

3、先进封装市场规模

摩尔定律的放缓、异质集成和各种大趋势(包括 5G、AI、HPC、物联网等)推动着先进封 装市场强势发展。根据 Yole 的数据,2019 年全球先进封装市场规模约 290 亿美元,预计 2025 年增长到 420 亿美元,年均复合增速约 6.6%,高于整体封装市场 4%的增速和传统封装市场 1.9% 的增速。

从下游应用市场来看,移动设备和消费电子对集成度要求高,是先进封装最大的细分市场, 2019 年占比达 85%,2019-2025 的 CAGR 为 5.5%,略低于整体增速,2025 年将占先进封装 市场的 80%。电信和基础设施是先进封装市场中增长最快的细分市场,CAGR 约为 13%,市场 份额将从 2019 年的 10%增至 2025 年的 14%。汽车与运输细分市场在 2019 年至 2025 年期间将以10.6%的 CAGR 增长,到 2025 年达到约 19 亿美元,但其在先进封装市场中所占的份额仍 将持平,约 4%。

从技术分类来看,3D 堆叠封装、嵌入式芯片封装、扇出型封装在 2019 年到 2025 年的增速 更高,CAGR 分别为 21%、18%、16%。扇出型技术进入移动设备、网络和汽车领域;3D 堆叠 技术进入 AI/ML、HPC、数据中心、CIS、MEMS/传感器领域;嵌入式芯片封装进入移动设备、 汽车和基站领域。

从先进封装收入构成来看,倒装技术占比遥遥领先,2018 年占比 81%。

从晶圆数来看,2019 年约 2900 万片晶圆采用先进封装,到 2025 年增长为 4300 万片,年 均复合增速为 7%。其中倒装技术占比最高,3D 封装增速最快。